### Automatic Generation of SystemVerilog Models from Analog/Mixed-Signal Circuits: A Pipelined ADC Example

Prof. Jaeha Kim Seoul National University & Scientific Analog, Inc. September 2021

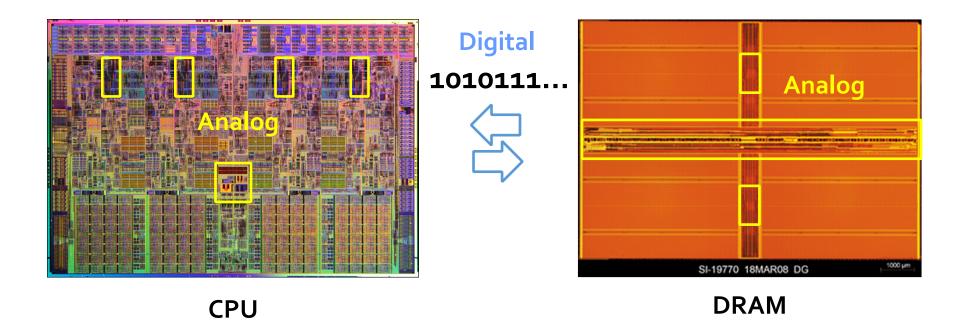

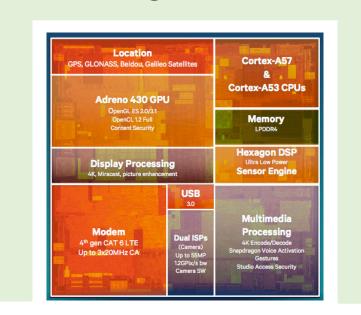

# Today SoC's are Mixed-Signal

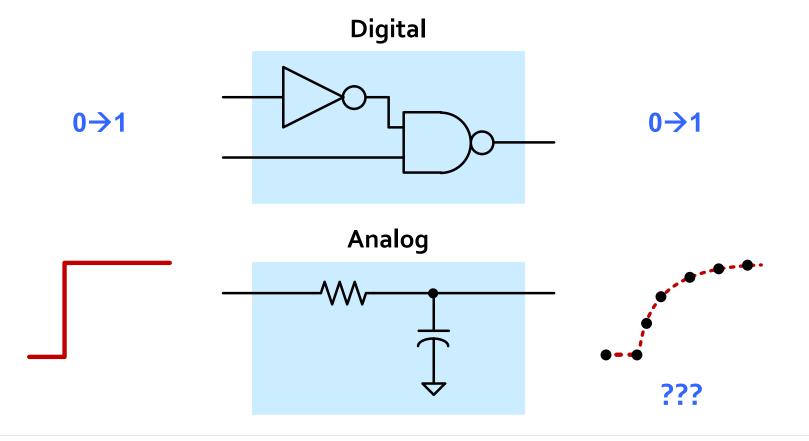

- No SoC's are purely digital or purely analog

- Many SoC's are digital on outside and analog on inside

- Chip-level testbenches are usually in SystemVerilog (UVM)

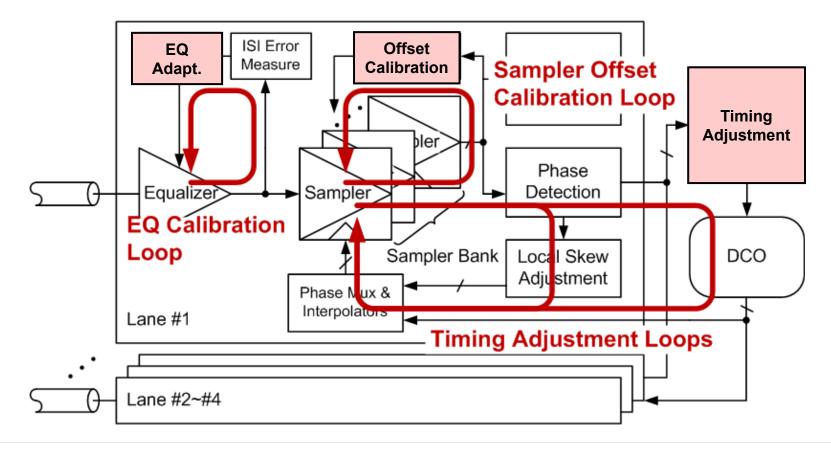

# With No Clear A/D Boundaries

• Often, analog and digital parts form a feedback loop; making it difficult to verify one without the others

# Goal: Verify SoC's in SystemVerilog

- To achieve this goal, we need capabilities to:

- Simulate analog models in SystemVerilog

- Auto-extract models from analog circuits

### SystemVerilog Testbench (UVM)

### **XMODEL:** Enable Analog for SV/UVM

- A plug-in extension that enables *fast and accurate analog/mixed-signal* simulation in *SystemVerilog*

- Event-driven: 10~100x faster than Real-Number Verilog

- Analog: supporting both functional and circuit-level models

- SystemVerilog: enabling analog verification in UVM

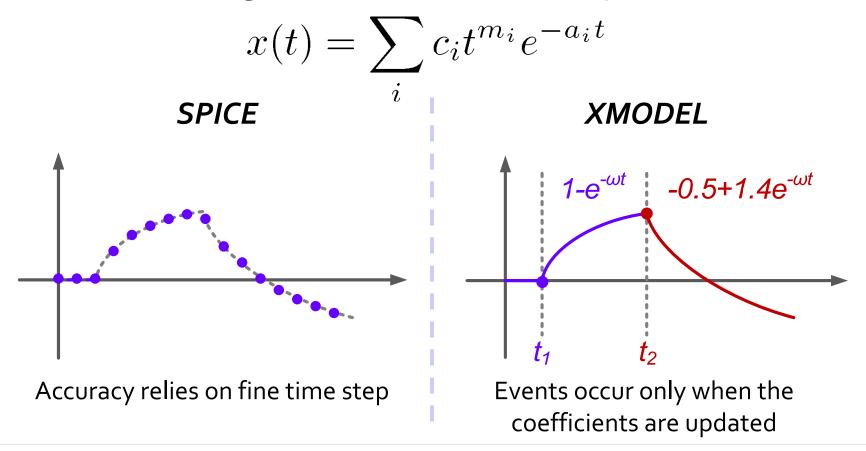

# **Event-Driven Simulation of Analog**

How do we extend the Verilog's event-driven algorithm to simulating analog circuits?

# **Expressing Analog Events**

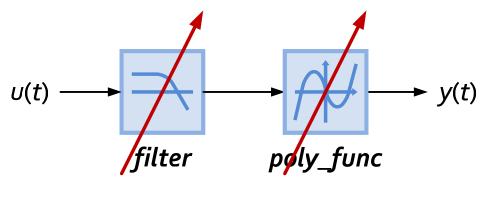

• *XMODEL* expresses analog signals in functional forms instead of using a series of time-value pairs:

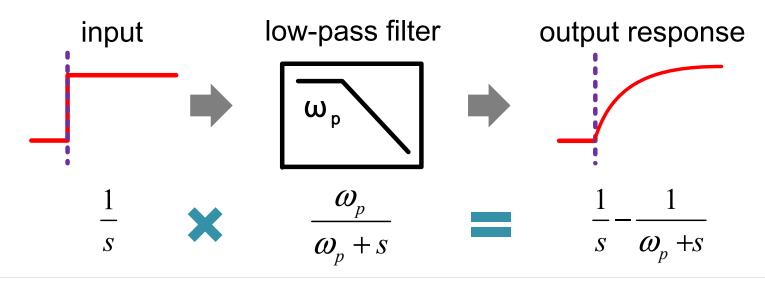

# **Propagating Analog Events**

• With the signals transformed into Laplace s-domain:

$$x(t) = \sum_{i} c_i t^{m_i - 1} e^{-a_i t} u(t) \xrightarrow{\mathcal{L}} X(s) = \sum_{i} \frac{b_i}{(s + a_i)^{m_i}}$$

• The response of a system can be computed in an eventdriven manner without time-step integration:

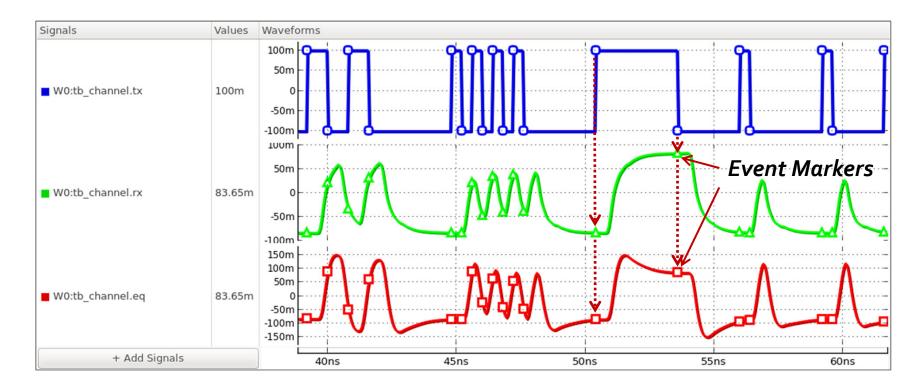

### **XMODEL's Event-Driven Simulation**

• XMODEL triggers very few events during simulation and hence achieves very fast speed

## **Block-Level vs. Circuit-Level Models**

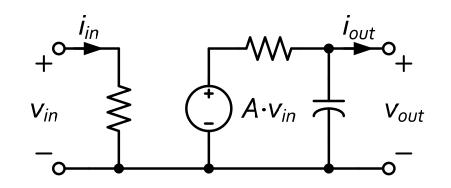

**Block-Level Model** (Signal-flow Model)

A network of blocks where signals flow in one direction only **Circuit-Level Model** (Conservative System Model)

- A network of circuits whose state is described by voltages & currents

- e.g. loading effects

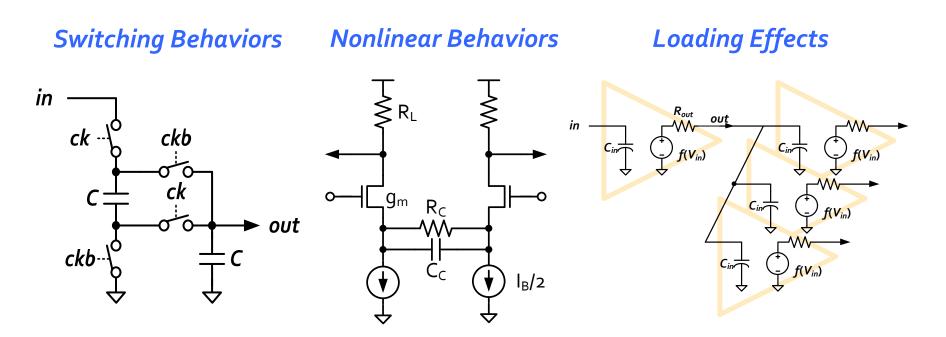

## **Need for Circuit-Level Models (CLMs)**

Circuit-level models are the most natural way to model switching, nonlinear, and loading effects in analog circuits

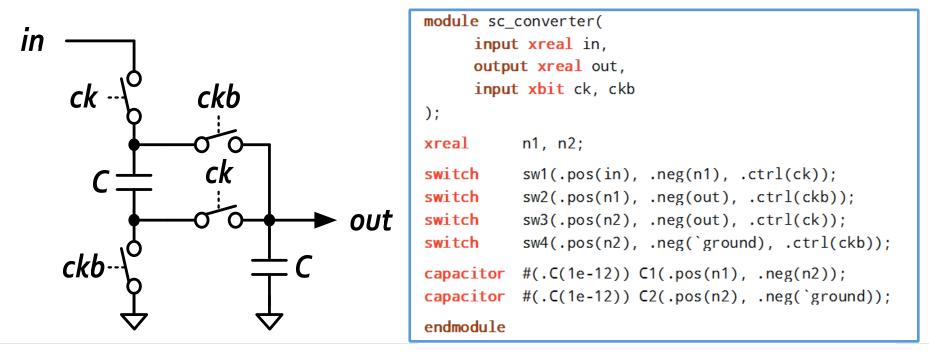

# **CLM Support in XMODEL**

- In *XMODEL*, one can describe analog circuits directly by listing the circuit's elements and devices

- *XMODEL* can simulate these models in SystemVerilog in event-driven fashion without invoking SPICE

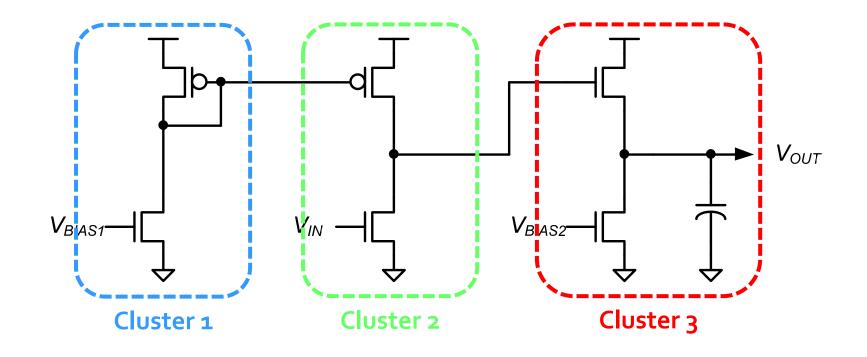

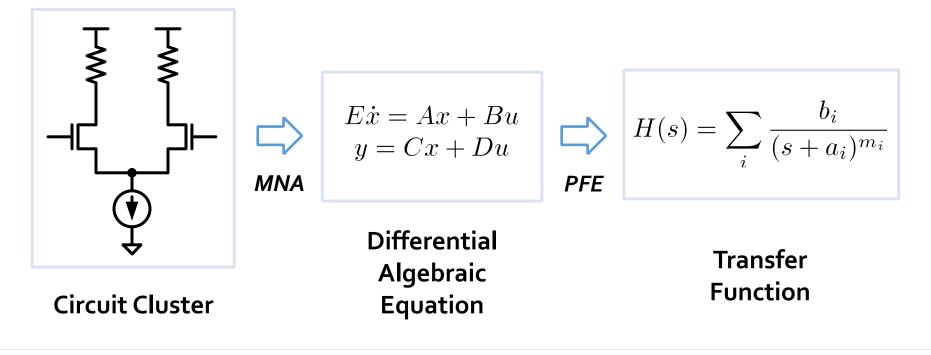

# CLM Support (1): Circuit Clustering

- *XMODEL* partitions the circuit into clusters that can be solved separately

- Signals across the cluster boundaries are unidirectional

## CLM Support (2): TF Extraction

- For each cluster, *XMODEL* extracts the transfer function (TF) between its inputs and outputs

- Then, the *XMODEL*'s event-driven algorithm can compute output events from the input events

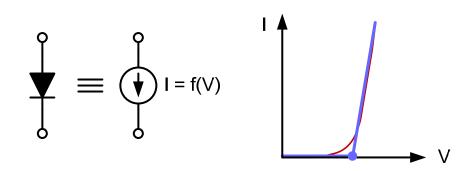

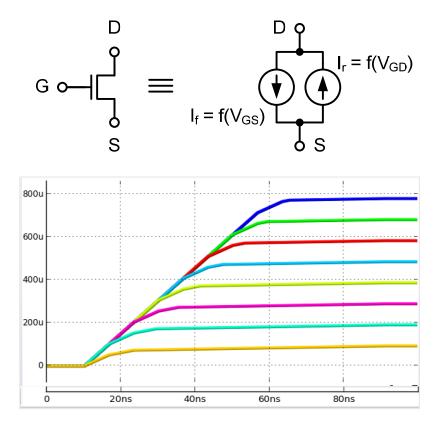

## **PWL Models for Nonlinear Elements**

- *XMODEL* models nonlinear elements (e.g. diodes and transistors) using piecewise-linear (PWL) models

- In each operation region, the circuit yields a linear TF

- Switch into a new TF when the region changes

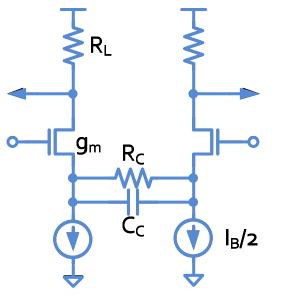

### **Structural Model Generation**

- The first way to auto-generate models from circuits

- Model each device in the circuit individually

- Build the circuit model by connecting the device models as in the original circuit

**SMODElementis**ives

|                             | e (<br>xreal inp, inn, // input signals<br>_xreal outp, outn // output signals                                           |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| xreal sp, sn;<br>xreal vdd; |                                                                                                                          |  |

| vsource                     | #(.mode("dc"), .dc(Vdd))<br>V1(.pos(vdd), .neg(~ground), .in(~ground));                                                  |  |

| isource                     |                                                                                                                          |  |

| nmosfet                     | <pre>#(.Kp(Gm), .Vth(Vth)) M1(.d(outn), .g(inp), .s(sp), .b(`ground)), M2(.d(outp), .g(inn), .s(sn), .b(`ground));</pre> |  |

| resistor                    | <pre>#(.R(Rload)) RL1(.pos(vdd), .neg(outp)), RL2(.pos(vdd), .neg(outn));</pre>                                          |  |

| capacitor                   | <pre>#(.C(Cload)) CL1(.pos(vdd), .neg(outp)), CL2(.pos(vdd), .neg(outn));</pre>                                          |  |

|                             | #(.R(Rc)) RC1(.pos(sp), .neg(sn));<br>#(.C(Cc)) CC1(.pos(sp), .neg(sn));                                                 |  |

| endmodule                   |                                                                                                                          |  |

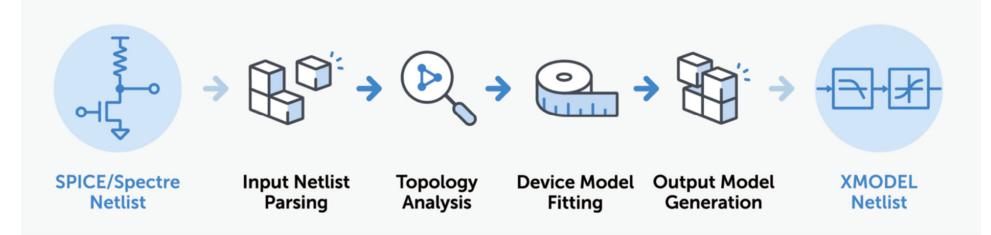

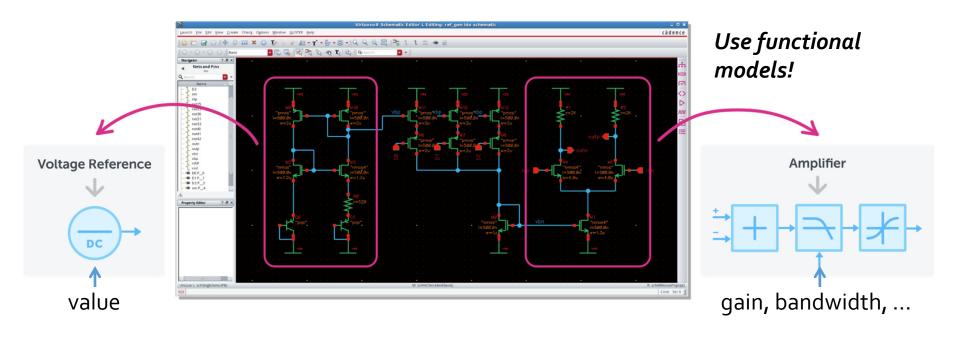

### **MODELZEN: Extract Bottom-Up Models**

- **MODELZEN** can automatically generate bottom-up analog models from your circuit schematics or netlists

- Extracts structural, circuit-level models by default

- Model parameters are calibrated via SPICE simulations

- Extracted models also simulate in an event-driven way

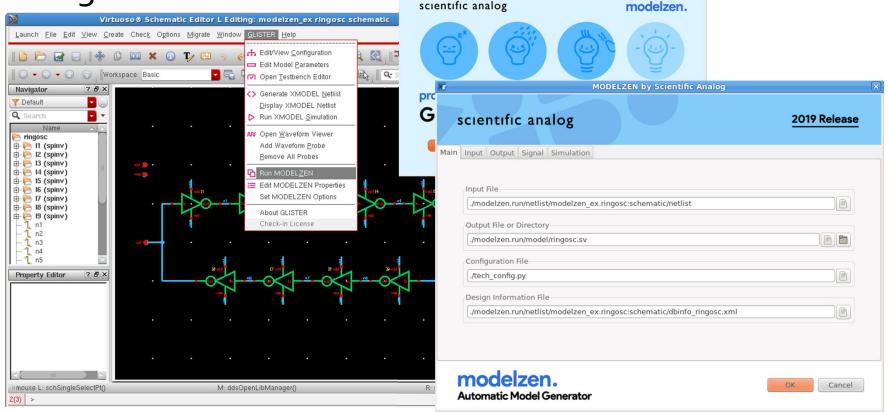

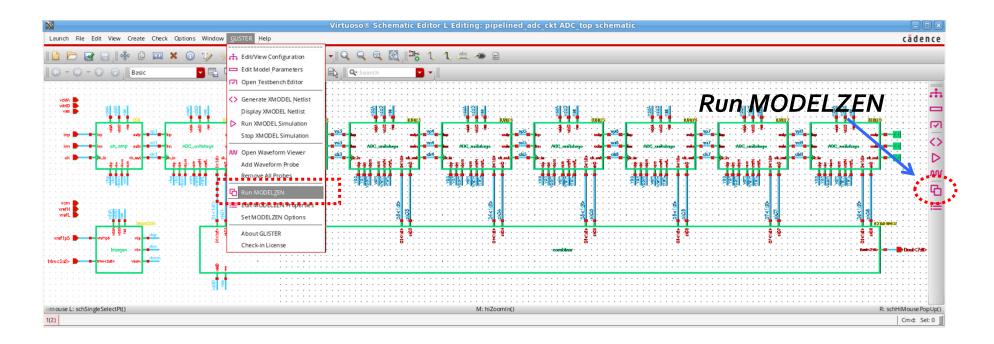

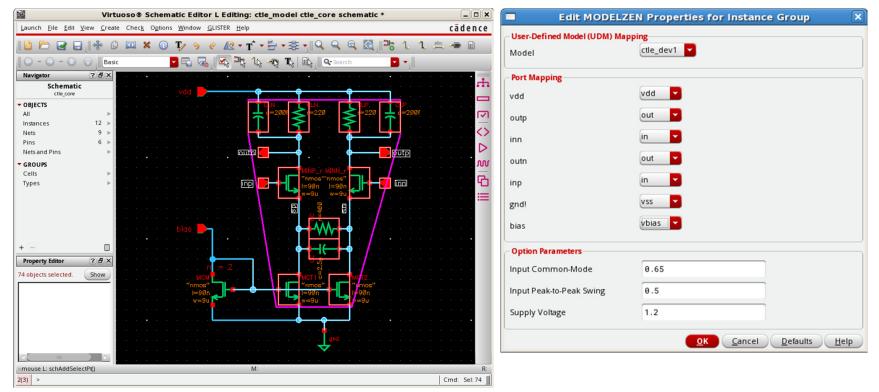

### **MODELZEN** in Cadence Virtuoso

• With *GLISTER* and *MODELZEN*, you can auto-create analog models from circuit schematics with just a single mouse click!

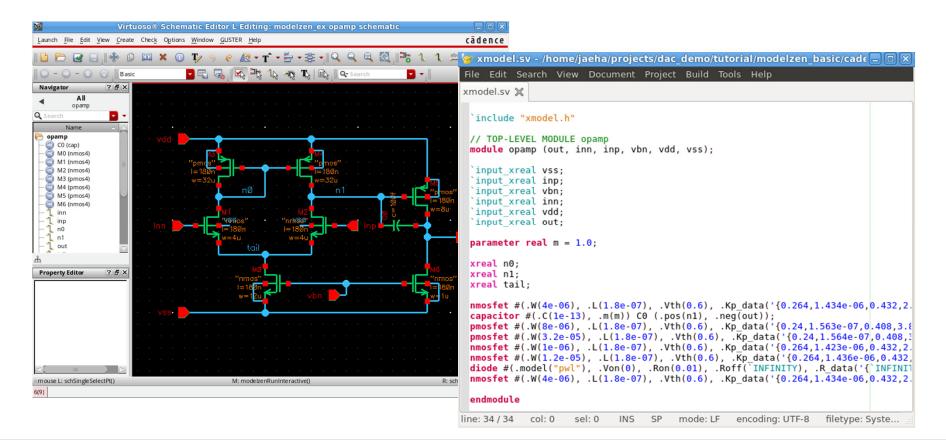

## Two-Stage Op Amp Example

MODELZEN generates correct-by-construction, structural models using circuit-level primitives

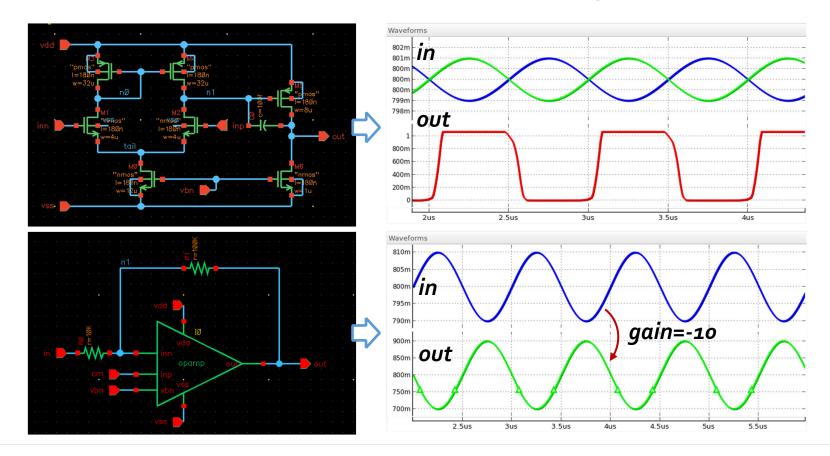

# **Op Amp Simulation Results**

• Models both nonlinear behavior when it's in open loop and linear behavior when in closed-loop feedback

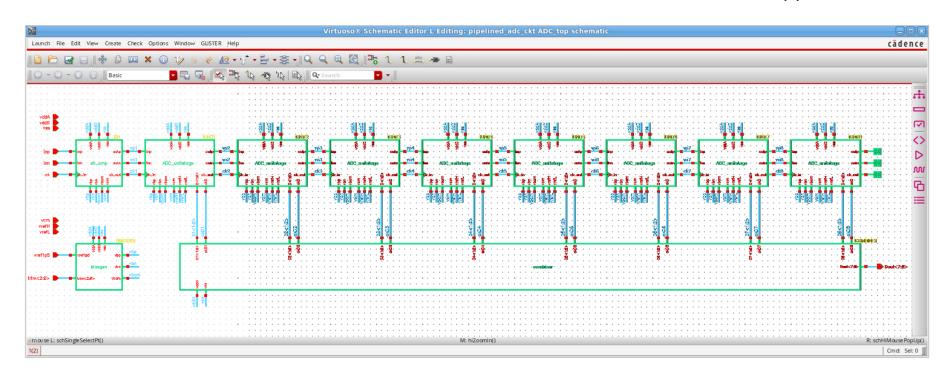

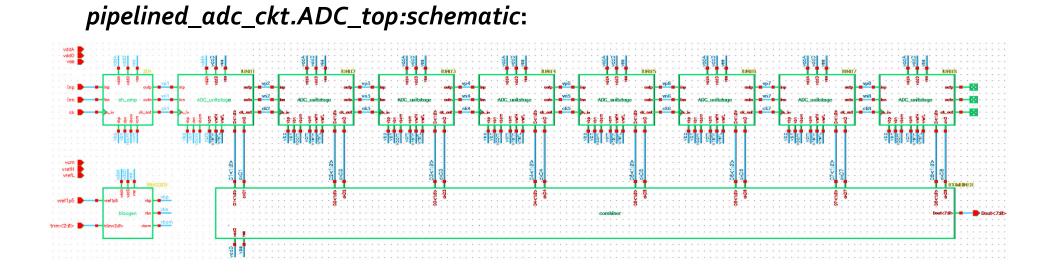

### **Pipelined ADC Example**

- An 8-bit pipelined ADC designed in PTM 45nm with dual power supplies (*vddD*=1.2V and *vddA*=3.3V)

- Operates at 100MHz with full-scale range of  $0.5V_{pp}$

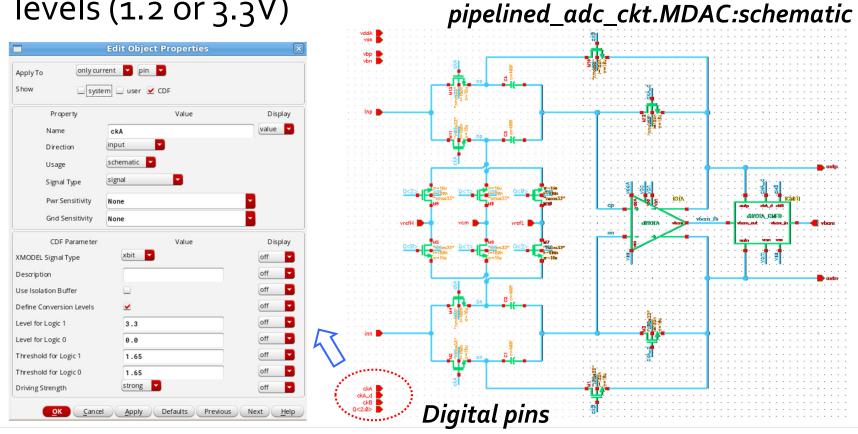

### CLM Extraction Approach (1)

Assign MODELZEN pin properties so that digital I/O pins have xbit or bit types with proper conversion levels (1.2 or 3.3V)

pipelined adc ckt.MDAC:schem

### CLM Extraction Approach (2)

- Specify a list of digital cells in *tech\_config.py* file so that *MODELZEN* can extract simpler models for them

- 1.2V logic gates: *std\_inv*, *std\_mux*, *std\_fulladd*, *std\_dff*, ...

- 3.3V logic gates: hv\_inv, hv\_nand2, hv\_nor2, hv\_xor, ...

- 1.2V ↔3.3V level converters: *conv\_hi2low, conv\_low2hi*

```

# subckt-specific device mapping

cells_digital = [

wildcard("std_*"),

wildcard("hv_*"),

wildcard("conv_*"),

]

devicemap_digital = derive_devicemap(devo_devicemap, convto_digital)

update_subcktmap(cells_digital, devicemap_digital)

```

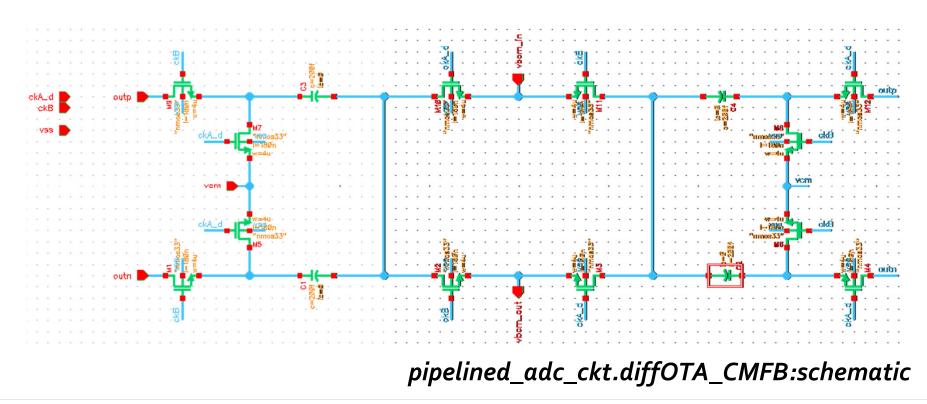

# CLM Extraction Approach (3)

- Specify a list of switch cells in *tech\_config.py* file so that their transistors can be extracted as switches

- e.g. switches used for switched-capacitor circuits

```

cells_switch = [

"diffOTA_CMFB",

"sh_amp",

"MDAC",

]

devicemap_switch = derive_devicemap(devo_devicemap, convto_switch)

update_subcktmap(cells_switch, devicemap_switch)

```

• Adding this option also helps:

```

devo_options['reduce_dev'] += ["nmosfet->switch", "pmosfet->switch"]

```

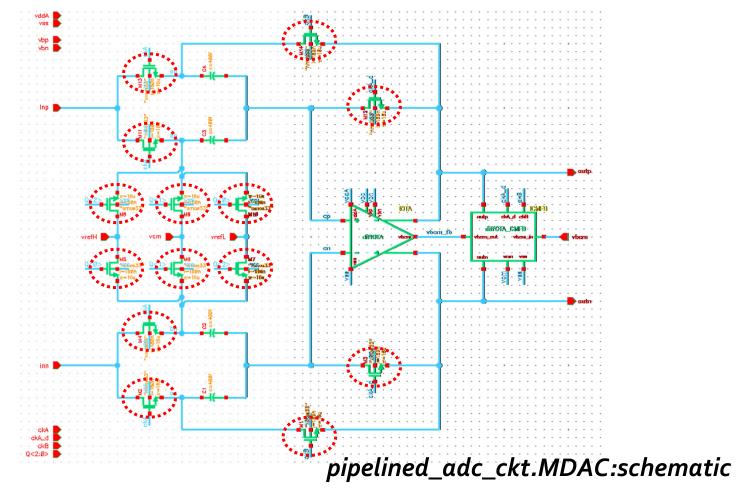

# CLM Extraction Approach (3): MDAC

• We want to model the transistors in MDAC as switches

### **Bottom-up Model Extraction**

- Just clicking "*Run MODELZEN"* icon on the top-level schematic extracts models from the entire circuit

- The extracted model is imported to an *xmodel* view

### **Extracted SystemVerilog Models**

### • pipelined\_adc\_ckt.ADC\_top:xmodel

| D// XMODEL/SystemVerilog model generated from ./modelzen.run/netlist/pipelined adc ckt.ADC         | // MODULE SUB ADC top conv hi2low                                                                       |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <pre>L// By MODELZEN (XMODEL Development Base) on Tue Aug 24 00:31:23 2021</pre>                   | <pre>module SUB_ADC_top_conv_hi2low (out, in, vddH, vddL, vss);</pre>                                   |

| `include "xmodel.h"                                                                                | <pre>`input_xreal vss;</pre>                                                                            |

|                                                                                                    | <pre>input_xreal vddL;</pre>                                                                            |

| // TOP-LEVEL MODULE ADC_top                                                                        | input_xreal vddH;                                                                                       |

| <pre>module ADC_top (Dout, ck, inn, inp, trim, vcm, vddA, vddD, vreflp5, vrefH, vrefL, vss);</pre> | input_xreal in;                                                                                         |

|                                                                                                    | `input_xreal out;                                                                                       |

| input_xbit_ck;                                                                                     | parameter real m = 1.0;                                                                                 |

| input [2:0] trim;                                                                                  | parameter reat m = 1.0;                                                                                 |

| input_xreal vddD;                                                                                  | xreal inb:                                                                                              |

| <pre>input_xreal vss;<br/>output [7:0] Dout;</pre>                                                 | xreal nd;                                                                                               |

| input xreal vddA;                                                                                  | xreal midb;                                                                                             |

| input xreal inp;                                                                                   |                                                                                                         |

| `input xreal inn;                                                                                  | SUB_ADC_top_hv_inv #(.wp(1.6e-06), .mult(1), .wn(8e-07), .m(m)) I1 (.out(inb), .in(in), .v              |

| `input xreal vrefL;                                                                                | SUB_ADC_top_std_inv #(.wp(4e-07), .mult(1), .wn(2e-07), .m(m)) I2 (.out(out), .in(midb), .              |

| `input_xreal vrefH;                                                                                | <pre>pmosfet #(.W(2e-07), .L(4.5e-08), .Kp(4.159e-05), .Vth(0.48), .Cgb('{1.016e-09,1.393e-09,1</pre>   |

| `input_xreal vcm;                                                                                  | <pre>nmosfet #(.W(1.6e-06), .L(1.8e-07), .Kp(4.208e-05), .Vth(0.924), .Cgb('{1.501e-09,1.998e-0</pre>   |

| `input_xreal vref1p5;                                                                              | <pre>pmosfet #(.W(2e-07), .L(4.5e-08), .Kp(4.159e-05), .Vth(0.48), .Cgb('{1.016e-09,1.393e-09,1</pre>   |

| parameter real m = 1.0;                                                                            | <pre>nmosfet #(.W(1.6e-06), .L(1.8e-07), .Kp(4.208e-05), .Vth(0.924), .Cgb('{1.501e-09,1.998e-6</pre>   |

|                                                                                                    | endmodule                                                                                               |

| xbit ck1;                                                                                          |                                                                                                         |

| xbit ck2;                                                                                          | (/ MODILE SUB ADC top conv. laudhi                                                                      |

| xbit ck3;                                                                                          | <pre>// MODULE SUB_ADC_top_conv_low2hi module SUB ADC top conv low2hi (out, in, vddH, vddL, vss);</pre> |

| xbit ck4;                                                                                          | module sub_abc_top_conv_tow2n1 (out, in, vade, vade, vss);                                              |

| xbit ck5;<br>xbit ck6;                                                                             | `input xreal vss;                                                                                       |

| Abit cK7:                                                                                          | input xreal vdd;                                                                                        |

| xbit ck8:                                                                                          | `input_xreal vddH;                                                                                      |

| wire ckd1:                                                                                         | `input_xreal in;                                                                                        |

| wire ckd2;                                                                                         | `input_xreal out;                                                                                       |

| wire ckd3;                                                                                         |                                                                                                         |

| wire ckd4;                                                                                         | parameter real m = 1.0;                                                                                 |

| wire ckd5;                                                                                         |                                                                                                         |

| wire ckd6;                                                                                         | <pre>xreal inb;<br/>xreal mid:</pre>                                                                    |

| wire ckd7;                                                                                         | xreal mid:<br>xreal mid:                                                                                |

| wire ckd8;<br>wire [1:0] d1;                                                                       | xreal net022;                                                                                           |

| wire [1:0] d1;<br>wire [1:0] d2;                                                                   | xreal net023;                                                                                           |

| wire [1:0] d2;                                                                                     |                                                                                                         |

| wire [1:0] d4;                                                                                     | <pre>nmosfet #(.W(4e-07), .L(4.5e-08), .Kp(8.887e-05), .Vth(0.408), .Cgb('{9.69e-10,1.39e-09,1.</pre>   |

| wire [1:0] d5;                                                                                     | SUB ADC top std inv #(.wp(4e-07), .mult(1), .wn(2e-07), .m(m)) II (.out(inb), .in(in), .vd              |

| wire [1:0] d6;                                                                                     | SUB_ADC_top_hv_inv #(.wp(1.6e-06), .mult(1), .wn(8e-07), .m(m)) I2 (.out(out), .in(midb),               |

| wire [1:0] d7;                                                                                     | <pre>nmosfet #(.W(1.6e-06), .L(1.8e-07), .Kp(4.208e-05), .Vth(0.924), .Cgb('{1.501e-09,1.998e-0</pre>   |

| wire [1:0] d8;                                                                                     | <pre>pmosfet #(.W(8e-07), .L(1.8e-07), .Kp(2.554e-05), .Vth(1.188), .Cgb('{1.327e-09,1.792e-09,</pre>   |

| xbit_net47;                                                                                        | <pre>nmosfet #(.W(1.6e-06), .L(1.8e-07), .Kp(4.208e-05), .Vth(0.924), .Cgb('{1.501e-09,1.998e-0</pre>   |

| xreal net48;                                                                                       | pmosfet #(.W(8e-07), .L(1.8e-07), .Kp(2.554e-05), .Vth(1.188), .Cgb('{1.327e-09,1.792e-09,              |

| xreal net49;                                                                                       | <pre>nmosfet #(.W(4e-07), .L(4.5e-08), .Kp(8.887e-05), .Vth(0.408), .Cgb('{9.69e-10,1.39e-09,1.</pre>   |

| xreal vbcm;                                                                                        | endmodule                                                                                               |

| xreal vbn;                                                                                         | entanoda ce                                                                                             |

| <pre>xreal vbp;<br/>xreal vnl;</pre>                                                               |                                                                                                         |

| xreal vn2;                                                                                         | // MODULE SUB ADC top diffOTA                                                                           |

| xreat vn3;                                                                                         | module SUB ADC top diffOTA (voutn, voutp, vbcm, vbn, vbp, vddA, vinn, vinp, vss);                       |

| xreal vn4;                                                                                         |                                                                                                         |

| xreal vn5;                                                                                         | <pre>`input_xreal vbcm;</pre>                                                                           |

| xreal vn6;                                                                                         | <pre>`input_xreal voutp;</pre>                                                                          |

| xreal vn7;                                                                                         | <pre>`input_xreal vss;</pre>                                                                            |

| xreal vn8;                                                                                         | `input_xreal vddA;                                                                                      |

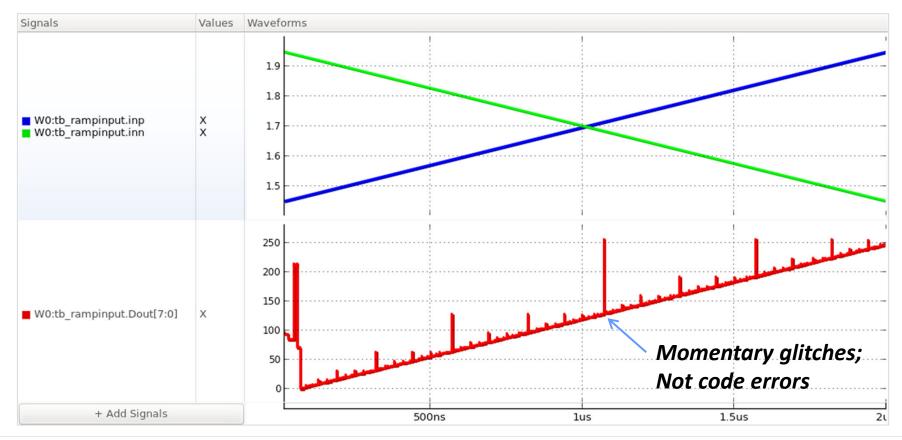

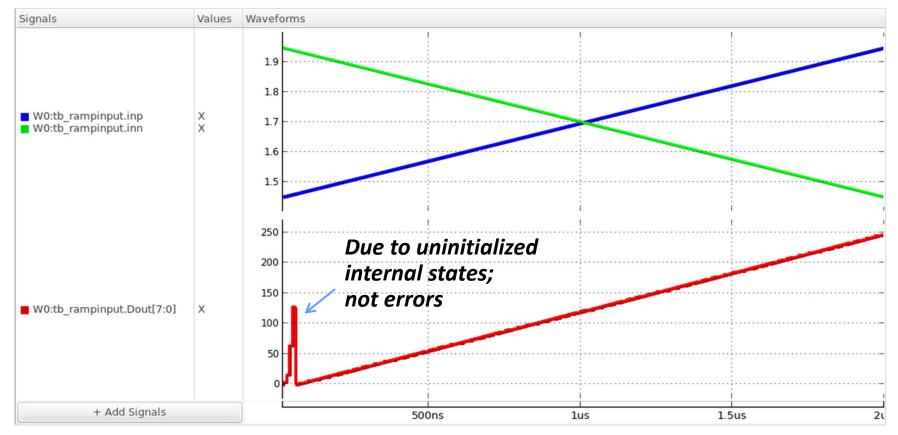

### Simulated Results: *tb\_rampinput*

### • pipelined\_adc\_ckt.ADC\_top:tb\_rampinput

• Simulation runtime: ~19 min.

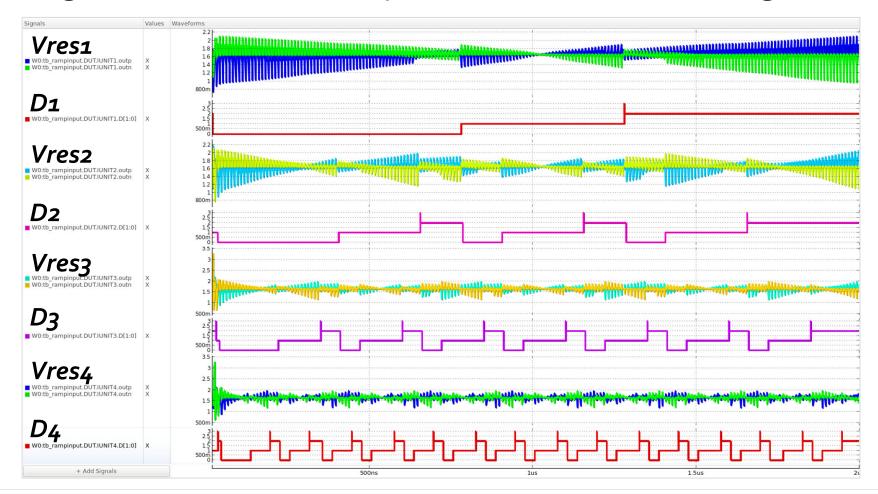

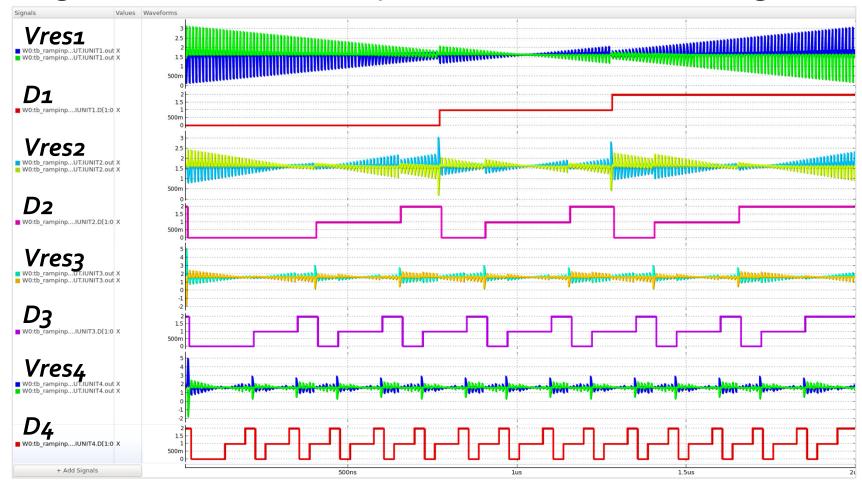

# Simulated Results: *tb\_rampinput* (2)

• Digital and residual outputs of the individual stages:

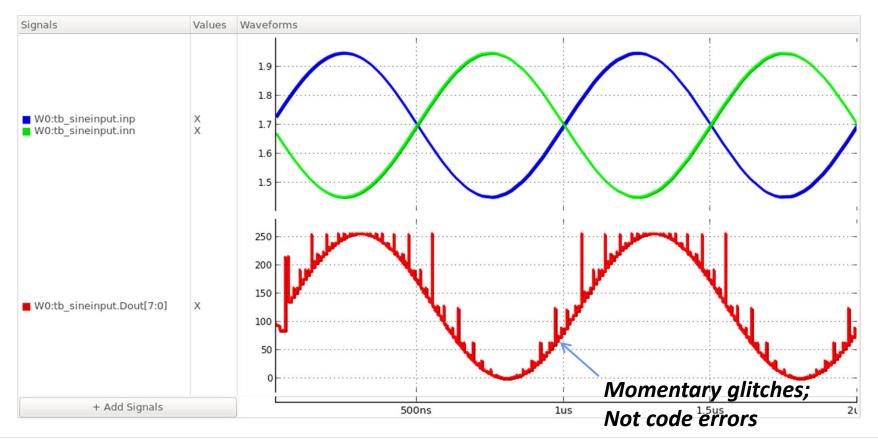

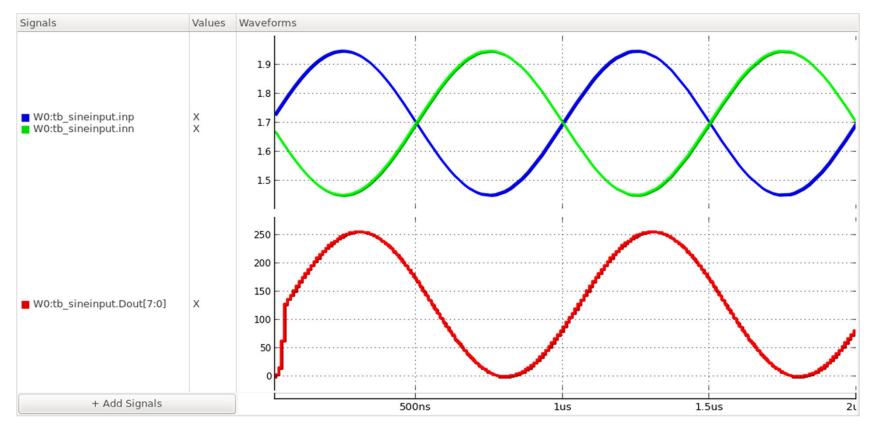

### Simulated Results: tb\_sineinput

### • pipelined\_adc\_ckt.ADC\_top:tb\_sineinput

• Simulation runtime: ~20 min.

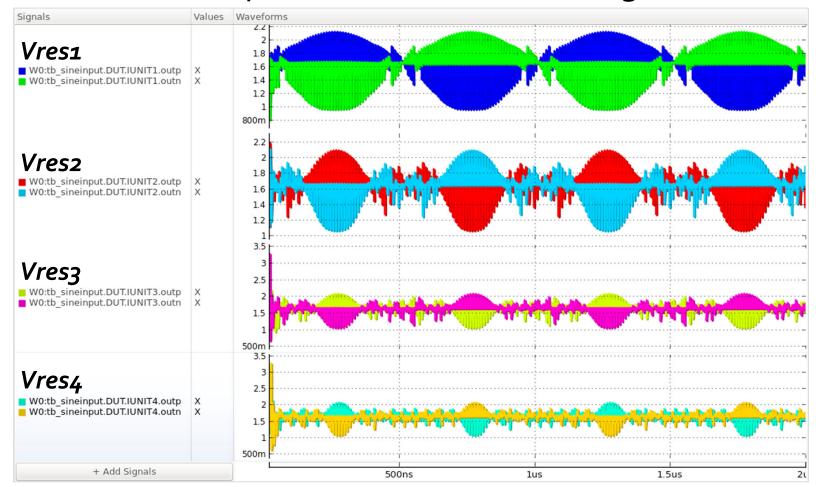

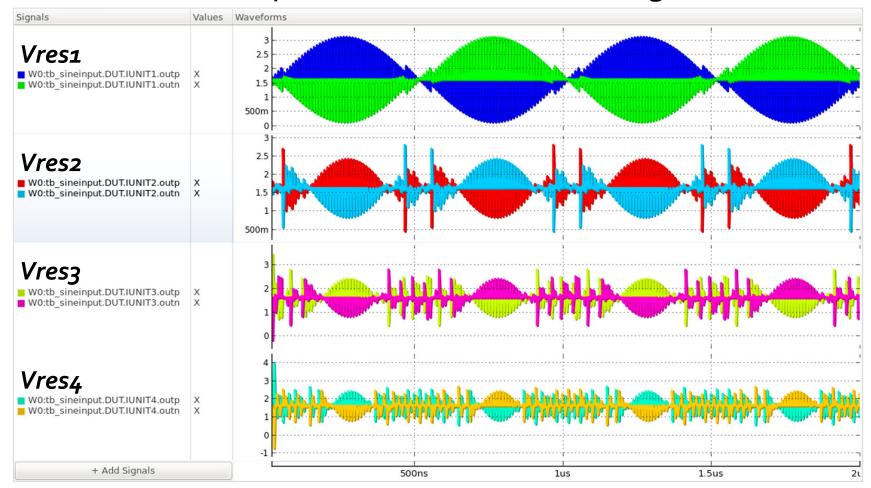

# Simulated Results: *tb\_sineinput* (2)

• The residual outputs of the individual stages:

### **Structural Model Generation**

- **Pros:** enables a **push-button flow** generating correctby-construction, SPICE-accurate analog models without requiring analog expertise

- Cons: the resulting circuit-level models are lowabstraction, transistor-based models that have limited simulation speeds

- Q: Can we generate *functional models* using the MODELZEN's push-button flow?

### **Functional Model Generation**

- Functional modeling focuses on the circuit's functions instead of its structure (i.e. topology):

- Choose a template model based on the circuit's functions

- Calibrate its model parameters via SPICE characterization

**Parameter Calibration**

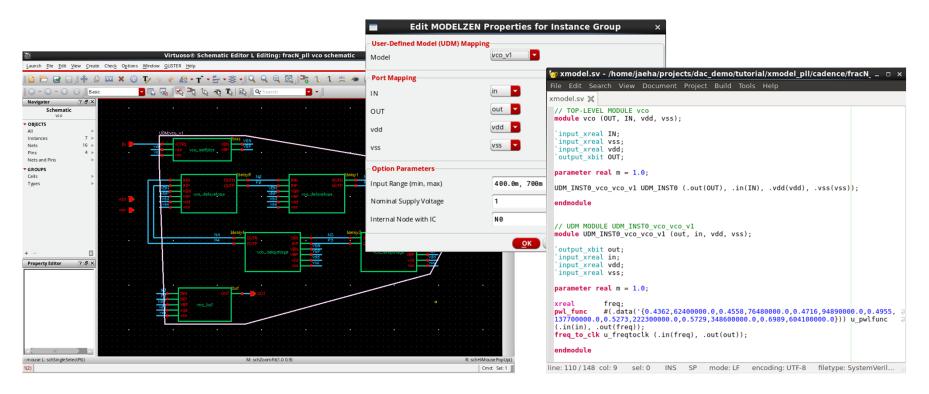

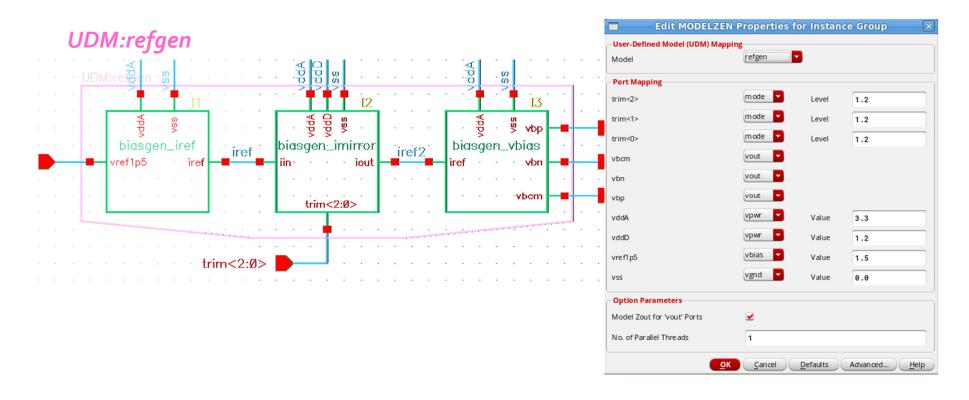

### **User-Defined Model (UDM)**

• The User-Defined Model (UDM) interface of MODELZEN lets you generate higher-abstraction models with SPICE-calibrated parameters for any selected parts of the circuits

# **Functional Modeling with UDM**

• For instance, you can auto-generate a functional model for an oscillator circuit of which frequency characteristics are calibrated by SPICE simulation

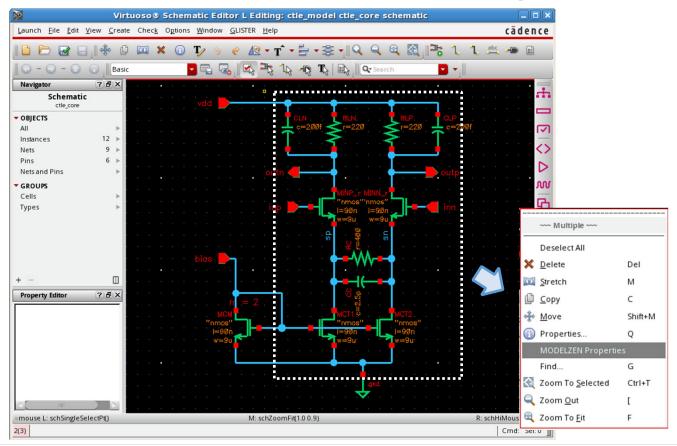

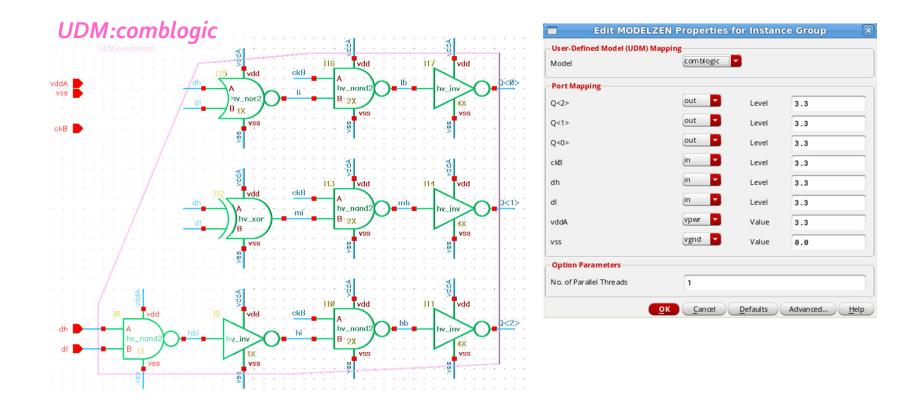

# **Defining UDM Mapping on Circuits**

• Select part of the circuits to be mapped to a UDM and right button click on **"MODELZEN Properties"**

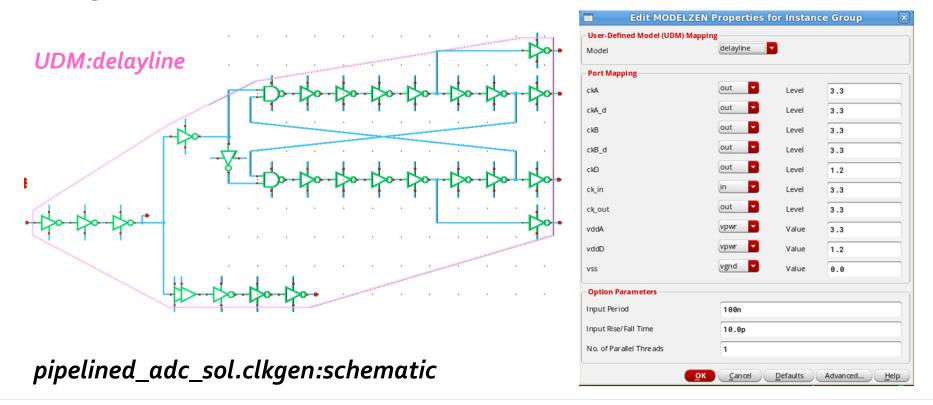

# Defining UDM Mapping on Circuits (2)

Edit MODELZEN Properties dialog window will appear where you can map each "pseudo-terminal" to a UDM port and define UDM parameters

## **UDM Definition**

- Each UDM is a Python class that defines:

- A list of terminals and option parameters

- Functional model template

- SPICE simulation steps to fit the model parameters

```

class pwm v1 (devo udm):

terms = {

'in'

: dict(direction="input", sigtype="xreal", width=1),

: dict(direction="output", sigtype="xbit", width=1),

'out'

'vpwr' : dict(direction="input", sigtype="xreal", width=1,

paramtype='real', prompt='Value', default=1.2),

'vgnd'

: dict(direction="input", sigtype="xreal", width=1,

paramtype='real', prompt='Value', default=0.0),

'vbias' : dict(direction="input", sigtype="xreal", width=[0,None],

paramtype='real', prompt='Value', default=0.7),

'ibias' : dict(direction="input", sigtype="xreal", width=[0,None],

paramtype='real', prompt='Value', default=0.0),

}

params = {

'range in' : dict(type="real array", prompt="Input Range (min, max)", default=[0.2,0.8]),

}

```

# **Quest for Analog Model Templates**

- Many circuits with analog inputs & outputs fall into:

- One-port model

- Multi-port impedance model

- Multi-port amplifier model

- Other circuits with digital inputs or outputs:

- Comparators and slicers

- Digital logic gates, flip-flops, and latches

- Delay lines and oscillators

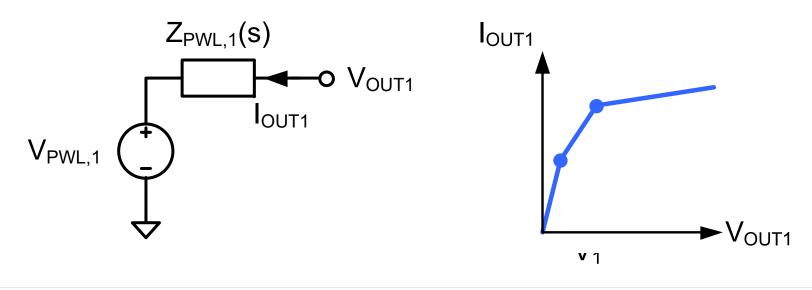

### **One-Port Model**

- For circuits producing voltages or currents without inputs (e.g. reference generators)

- Thevenin/Norton-equivalent circuit models finite R<sub>out</sub>

- $\bullet$  V1 and R1 can be PWL functions to model nonlinearity

- R<sub>1</sub> can be Z<sub>1</sub>(s) to model AC impedance

### **Flexible Port Widths**

- Many of our UDM ports have variable widths, so that each UDM can be mapped to a variety of circuits

- For example, our *refgen* UDM modeling one-port circuits can have arbitrary number of *vout*'s and *iout*'s

| UDM Port | Description        | Parameter                                           |

|----------|--------------------|-----------------------------------------------------|

| vout     | Voltage output     | lout bias                                           |

| iout     | Current output     | Vout bias                                           |

| mode     | Digital mode input | Voltage level<br>: <i>level1</i> [, <i>levelo</i> ] |

# **Digital Mode Inputs**

- Many analog circuits have *digital mode inputs* for various purposes: e.g. trimming, power-down, enable, ...

- These inputs don't change the model template, but change the model parameter values

- e.g. changing the output level or impedance

- Our UDMs support arbitrary number of **`mode'** inputs

- Generated model contains a look-up table defining parameter values for each combination of digital modes

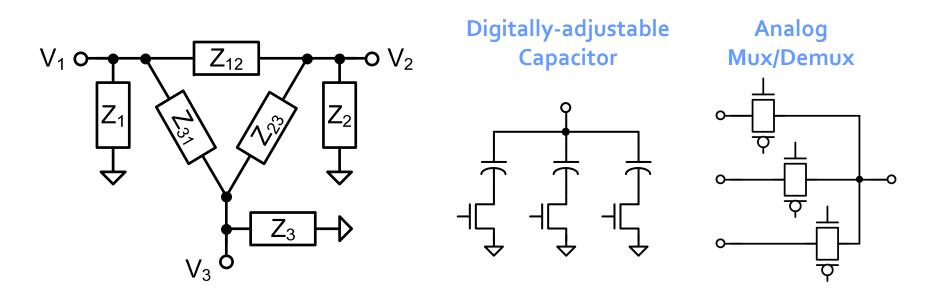

# **Multi-Port Impedance Model**

- For circuits having impedances between multiple ports

- Often, digital modes control their impedance values

- e.g. digitally-controlled resistors and capacitors, analog multiplexer/demultiplexers (switch networks)

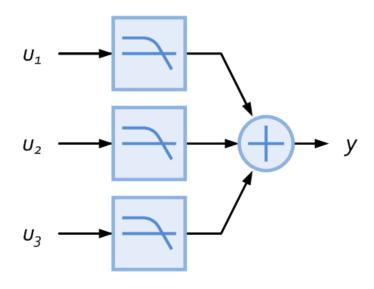

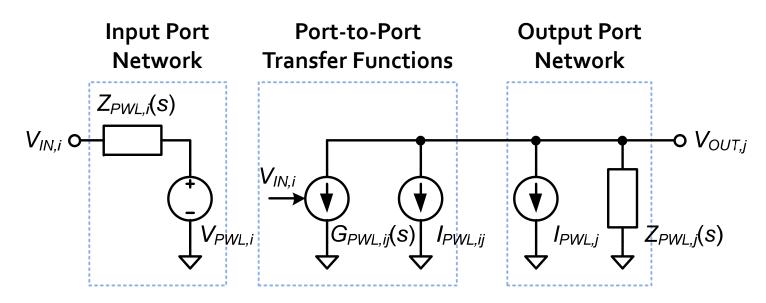

### **Multi-Port Amplifier Model**

- For circuits amplifying/filtering from inputs to outputs

- Each input/output port network with finite and/or nonlinear Z<sub>in</sub>(s) or Z<sub>out</sub>(s)

- Port-to-port transfer functions model DC gain, AC TF, and/or nonlinearity between input & output ports

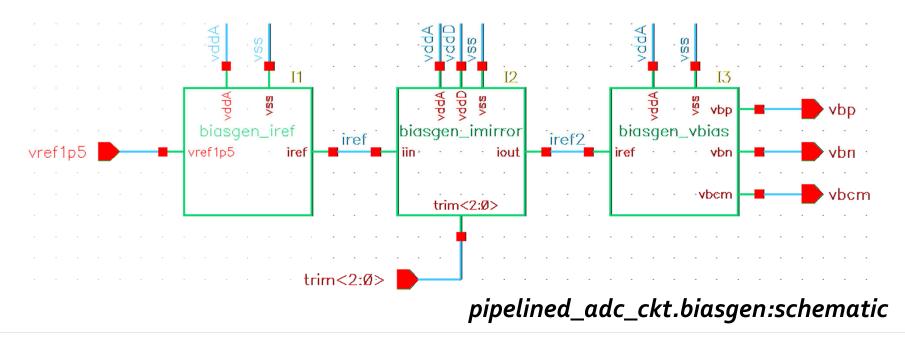

### **Bias Generator:** biasgen

- Generates digitally-trimmable bias voltages via:

- First stage generating a reference current (*iref*) from *vref*

- Second stage scaling the current with trim<2:0>

- Third stage converting the current into vbp, vbn & vbcm

# UDM refgen for biasgen

• Models a circuit generating reference voltages or currents controlled by digital *mode* inputs

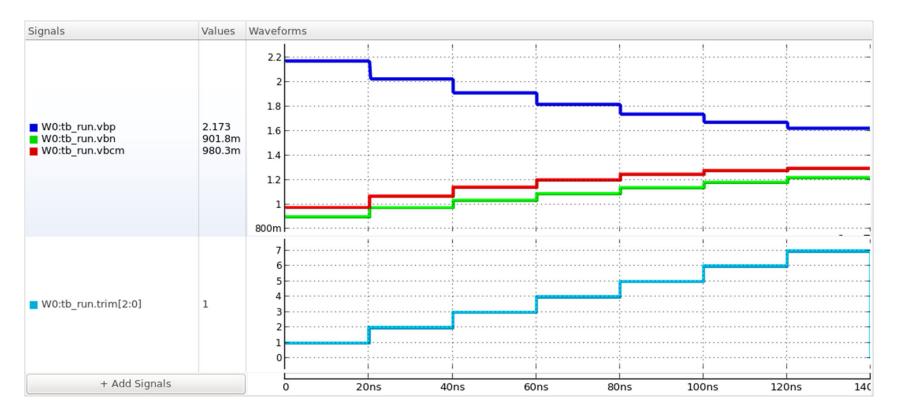

# Simulation Results: biasgen

- Testbench: *pipelined\_adc\_ckt.biasgen:tb\_run*

- Measuring the bias voltage levels while varying *trim*

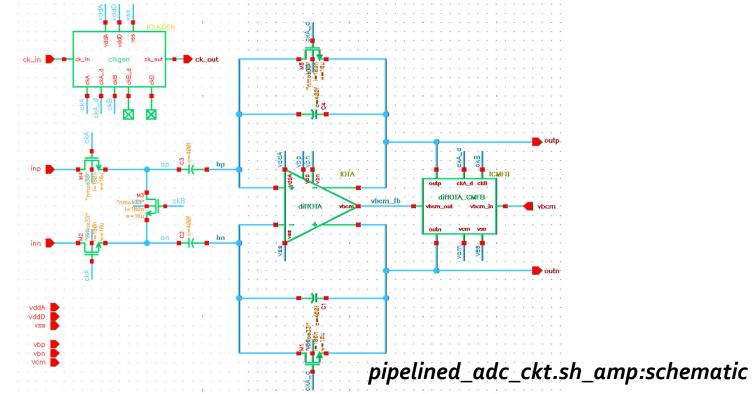

# Sample-and-Hold Stage: *sh\_amp*

- A switched-capacitor sample-and-hold amplifier

- A *common-mode feedback* (*CMFB*) circuit maintains the output common-mode level at *vcm*

48

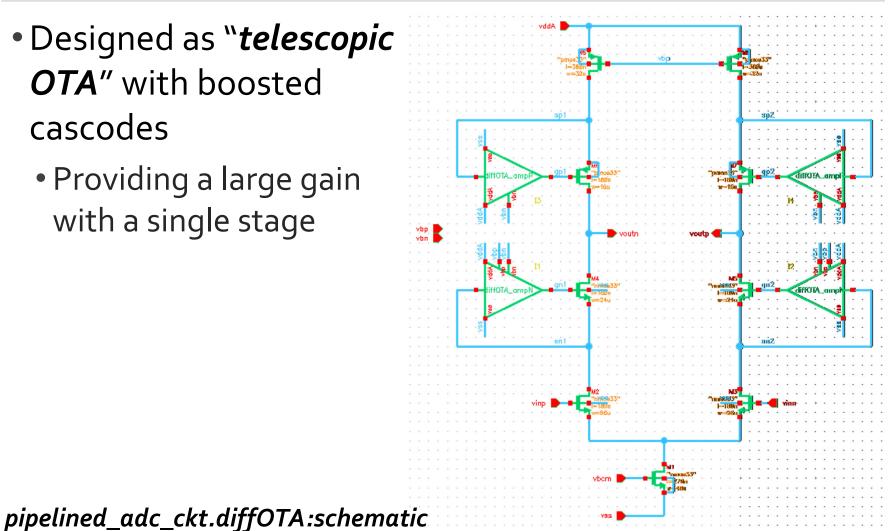

# **Differential OTA:** *diffOTA*

- Designed as "telescopic OTA" with boosted cascodes

- Providing a large gain with a single stage

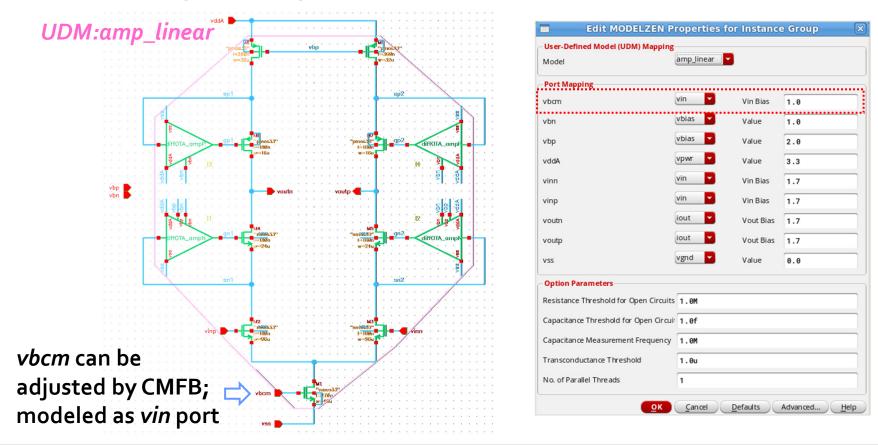

# UDM amp\_linear for diffOTA

Models linear amplifier networks with voltage or current input/output's

# CMFB Circuit: *diffOTA\_CMFB*

Applies an offset between vbcm\_in and vbcm\_out which is equal to the difference between the outp/outn common-mode level and vcm

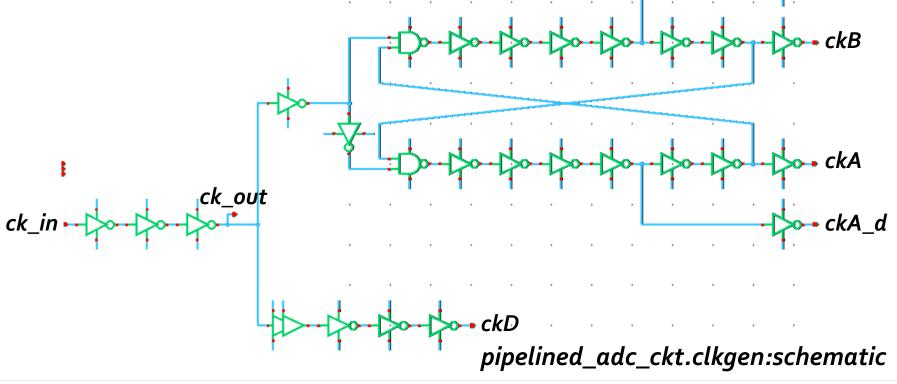

# **Clock Generator:** *clkgen*

• Inverter chains drive the clock loads and add delays defining the non-overlapping periods

• ckD has 1.2V swing; others have 3.3V

# UDM delayline for clkgen

Models a delay line with digital input/output's which can be gated or delay-adjusted depending on the digital *mode* inputs

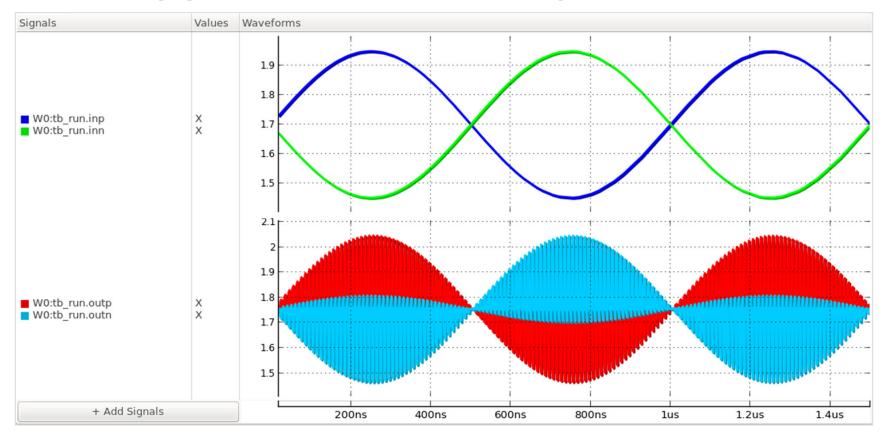

### Simulation Results: *sh\_amp*

- Now, generate a model for sh\_amp

- And run *pipelined\_adc\_ckt.sh\_amp:tb\_run*

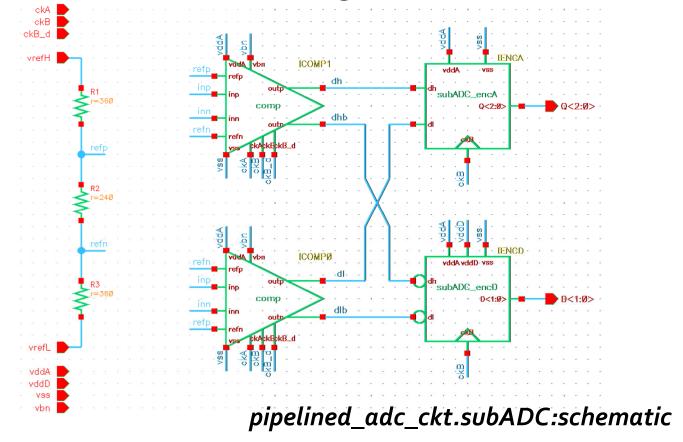

# 1.5-bit Sub-ADC: *subADC*

• A flash-type ADC made of R-string reference generator, comparators, and encoder logic

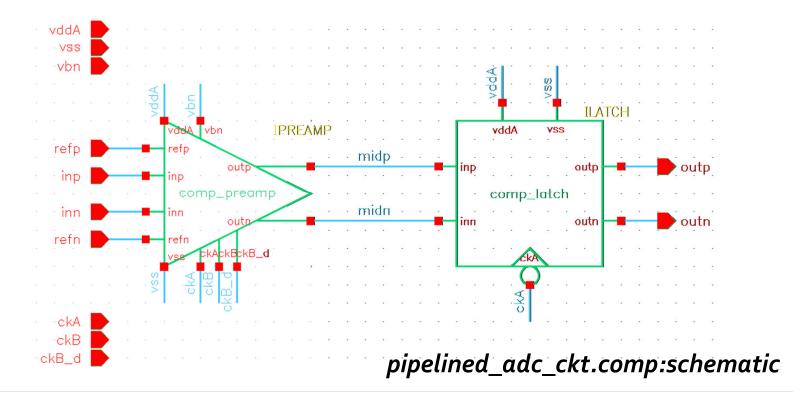

#### **Comparator Stage:** *comp*

• Made of a pre-amplifier stage amplifying the difference between V<sub>in</sub>=**inp**-**inn** and V<sub>ref</sub>=**refp**-**refn** and a clocked comparator (latch) stage detecting its polarity

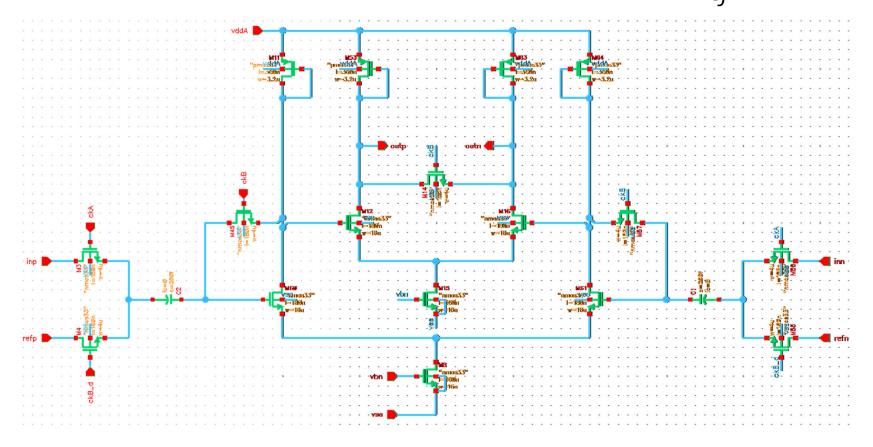

### **Pre-Amplifier Stage:** *comp\_preamp*

• A switched-capacitor circuit amplifying V<sub>in</sub>-V<sub>ref</sub>

pipelined\_adc\_ckt.comp\_preamp:schematic

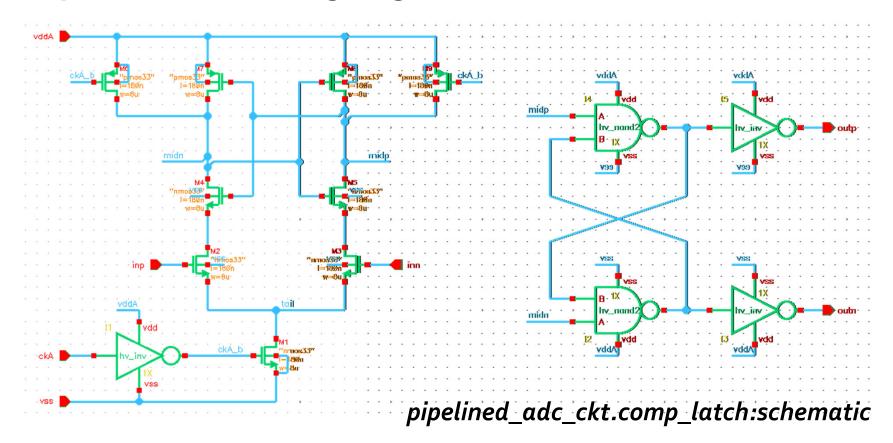

### Latch Stage: comp\_latch

A strongArm comparator detecting the polarity of inp-inn at the falling edge of ckA

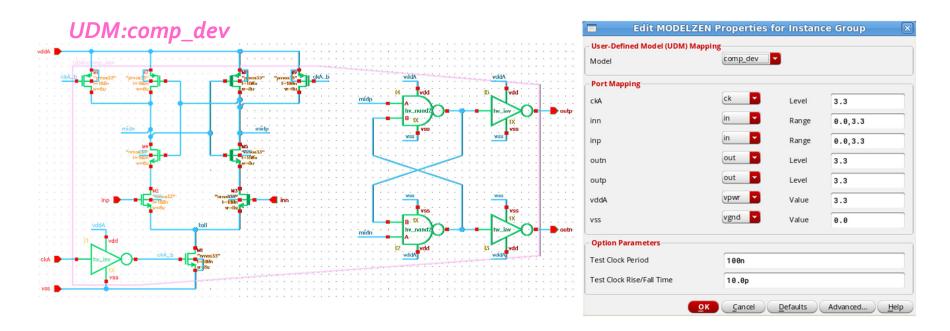

# UDM comp\_dev for comp\_latch

• A custom UDM that models a clocked comparator circuit with *xreal*-type analog inputs and *xbit*-type digital outputs

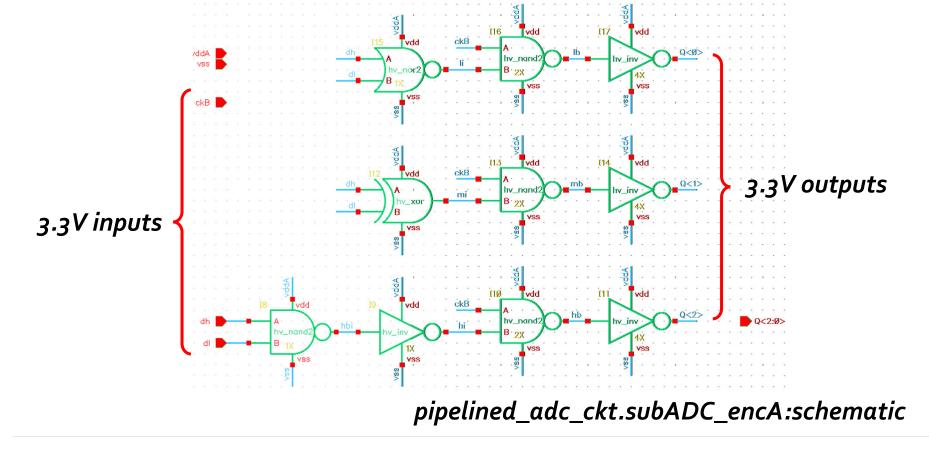

### Output Encoder Logic: subADC\_encA

60

• Converts the thermometer-coded inputs (*dh*, *dl*) to one-hot-coded outputs *Q*<2:0>, gated by *ckB*

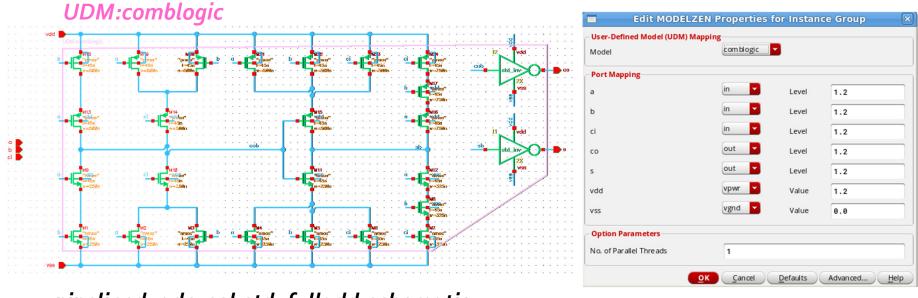

### UDM comblogic for subADC\_encA

• Models arbitrary combinational logic paths

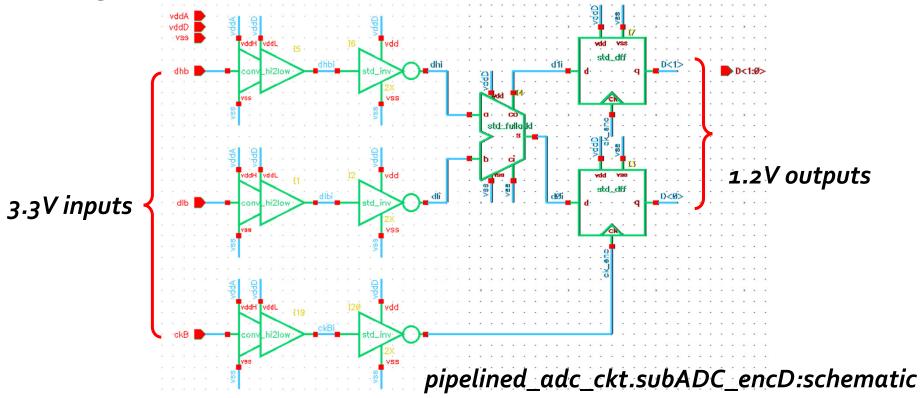

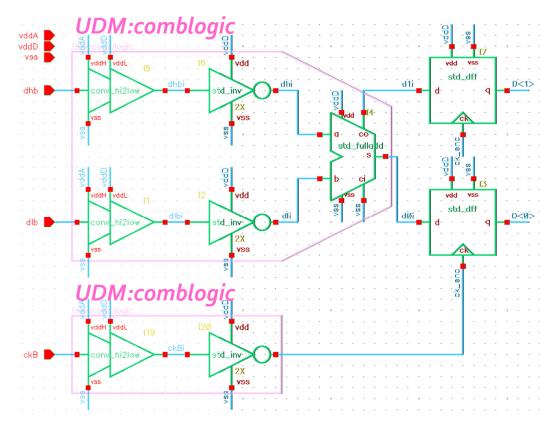

### **Output Encoder Logic:** *subADC\_encD*

Converts the thermometer-coded inputs (*dhb*, *dhl*) to binary-coded outputs *D<1:0>*, registered at falling edge of *ckB*

#### UDM comblogic for subADC\_encD

• Can also model level converters by setting input/output levels

| Model                   | comblogic |       |     |  |

|-------------------------|-----------|-------|-----|--|

| Port Mapping            |           |       |     |  |

| iOb                     | out       | Level | 1.2 |  |

| d1i                     | out       | Level | 1.2 |  |

| dhb                     | in 🔽      | Level | 3.3 |  |

| dlb                     | in 🔽      | Level | 3.3 |  |

| /ddA                    | vpwr 🔽    | Value | 3.3 |  |

| /ddD                    | vpwr 🔽    | Value | 1.2 |  |

| /55                     | vgnd 🔽    | Value | 0.0 |  |

| Option Parameters       |           | ·     |     |  |

| No. of Parallel Threads | 1         |       |     |  |

| User-Defined Model (UDM) N | C         | -     |     |  |

|----------------------------|-----------|-------|-----|--|

| Model                      | comblogic |       |     |  |

| Port Mapping               |           | ,     |     |  |

| c kB                       | in 🔽      | Level | 3.3 |  |

| ck_enc                     | out 🔽     | Level | 1.2 |  |

| vddA                       | vpwr 🔽    | Value | 3.3 |  |

| vddD                       | vpwr 🔽    | Value | 1.2 |  |

| vss                        | vgnd 🔽    | Value | 0.0 |  |

| Option Parameters          |           |       |     |  |

| No. of Parallel Threads    | 1         |       |     |  |

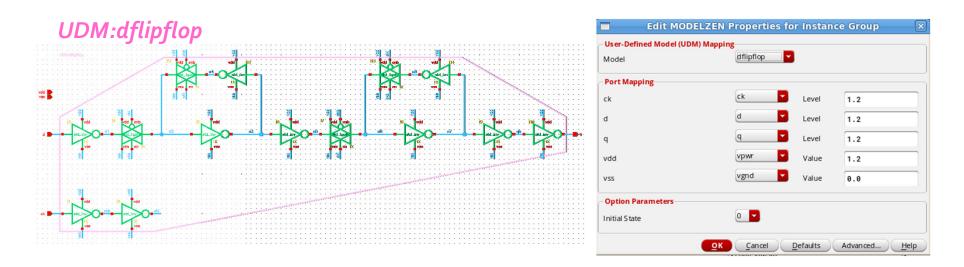

# UDM dflipflop for std\_dff

- Models D-flipflops with optional set/reset inputs

- Auto-detects clock, set/reset & output polarities, and sync/async types, ...

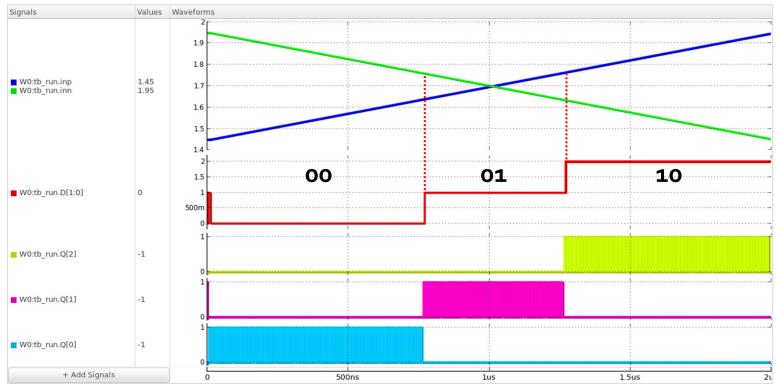

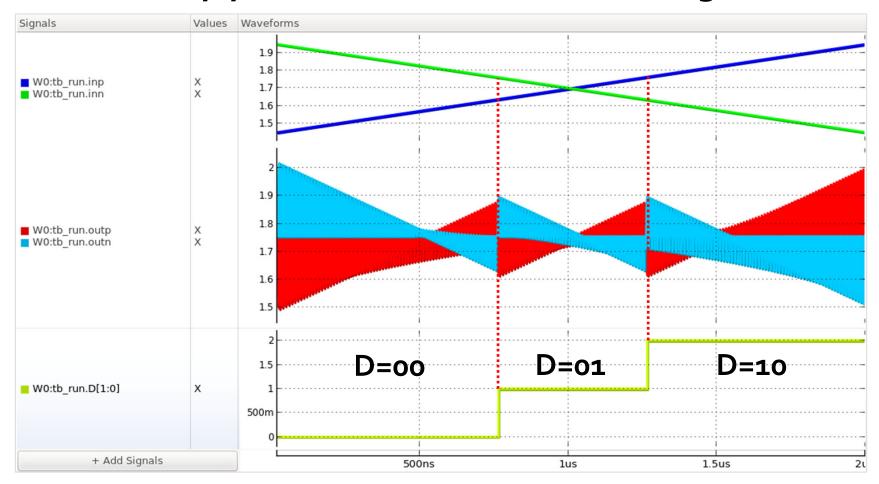

### Simulation Results: subADC

- Testbench: *pipelined\_adc\_ckt.subADC:tb\_run*

- Sub-ADC produces both binary-coded output **D<1:0>** and one-hot-coded output **Q<2:0>**

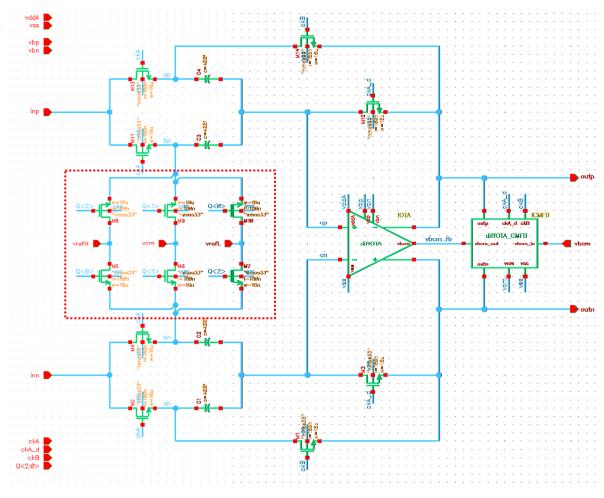

# 1.5-bit MDAC: MDAC

- Sub-DAC selects

vrefH, vcm, or

vrefL depending

on one-hot

coded Q<2:o>

- **Q<2:0>** is qualified by *ckB*

pipelined\_adc\_ckt.MDAC:schematic

### Simulation Results: MDAC

- Testbench: *pipelined\_adc\_ckt.MDAC:tb\_run*

- Confirms gain = 2 and offset =  $-V_{FS}/2$ , o, and  $+V_{FS}/2$

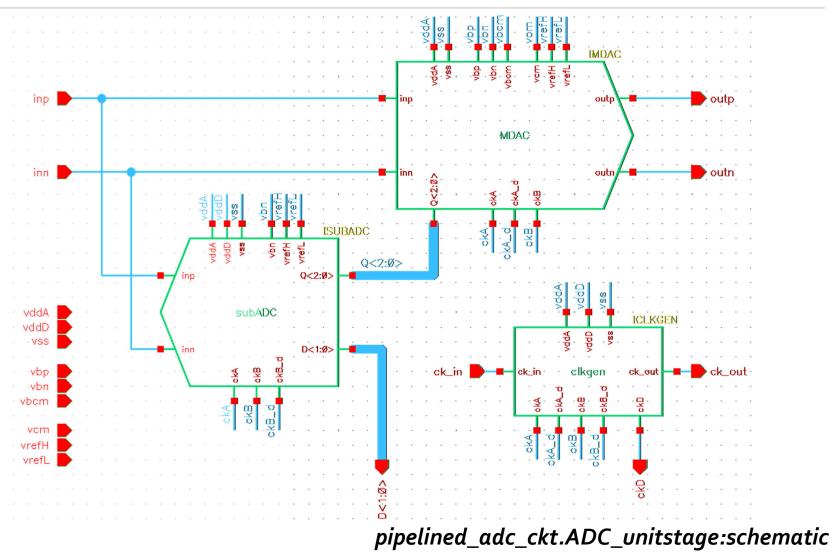

#### 1.5-bit Unit Stage: ADC\_unitstage

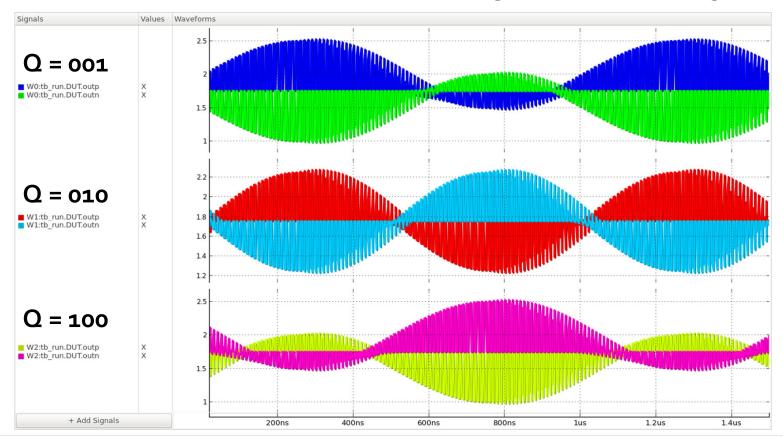

# Simulation Results: ADC\_unitstage

#### • Testbench: *pipelined\_adc\_ckt.ADC\_unitstage:tb\_run*

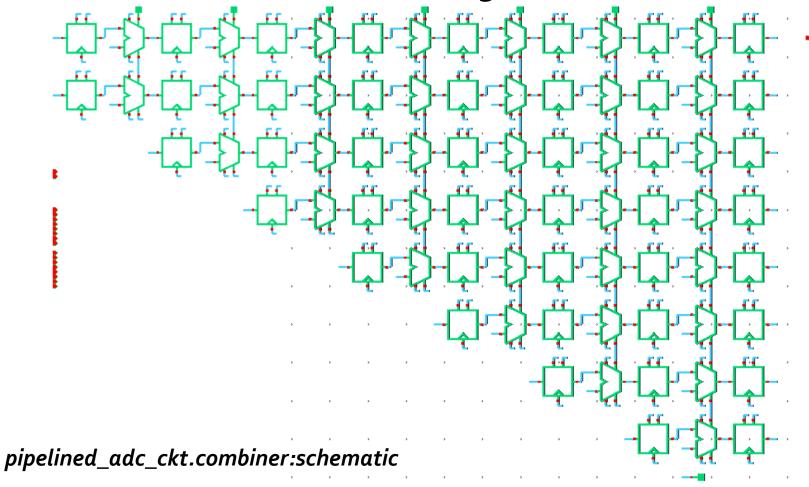

### **Digital Combiner:** *combiner*

• A cascade of shift-and-add stages

70

### UDM comblogic for std\_fulladd

#### • Static CMOS logic computing:

$$S = A \oplus B \oplus C_i$$

$C_o = AB + BC_i + C_iA$

pipelined\_adc\_sol.std\_fulladd:schematic

#### **—** 72

# Pipelined ADC: ADC\_top

• Now we are ready to extract the top-level model of the pipelined ADC!

#### Simulated Results: *tb\_rampinput*

#### • pipelined\_adc\_ckt.ADC\_top:tb\_rampinput

• Simulation runtime: 60 sec. (vs. 18.7 min. with CLM)

# Simulated Results: *tb\_rampinput* (2)

• Digital and residual outputs of the individual stages:

#### Simulated Results: tb\_sineinput

#### pipelined\_adc\_ckt.ADC\_top:tb\_sineinput

• Simulation runtime: 54 sec. (vs. 19.9 min. with CLM)

# Simulated Results: *tb\_sineinput* (2)

#### • The residual outputs of the individual stages:

# Summary

- Demonstrated two ways of automatically extracting bottom-up models from analog circuits

- Structural modeling guarantees correct-by-construction models for all kinds of circuits

- *Functional modeling* yields higher-abstraction models that run much faster

- Best results can be achieved by combining the two

- Now with the SystemVerilog models for analog circuits, you can perform efficient verification for mixed-signal SoC's all in SystemVerilog/UVM!