Webinar Series on

Webinar Series on

ANALOG VERIFICATION INSIGHTS

Harnessing the Power of UVM for AMS Verification with XMODEL

March 2, 2023 13:30-17:00 PM Pacific Time

DoubleTree by Hilton Hotel San Jose, CA

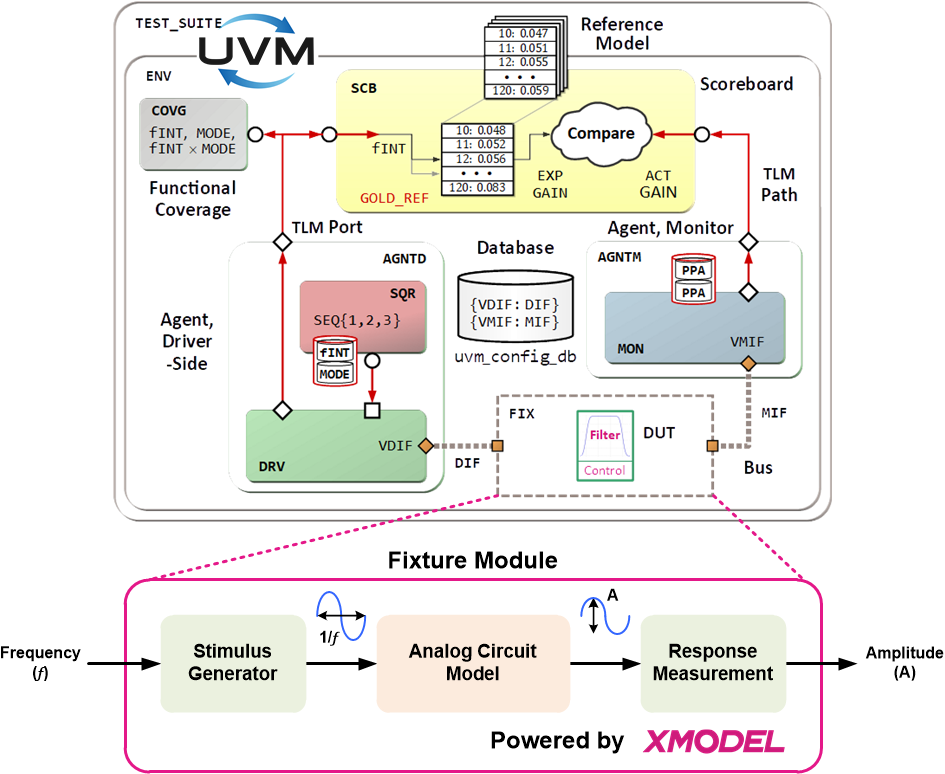

In this tutorial hosted by DVCon US 2023, you will learn how to write a UVM testbench for analog/mixed-signal circuits. UVM (Universal Verification Methodology) is a framework of standardized SystemVerilog classes for building reusable and scalable testbenches for digital systems, and we will show that it can be extended to verifying analog circuits simply by using a well-defined fixture module encapsulating the device-under-test (DUT) and its AMS instrumentations described with XMODEL primitives. Through a series of hands-on lab exercises using a digitally-programmable bandpass filter as an example, you will learn how to write a UVM testbench that measures the filter’s transfer gains at randomly-chosen frequencies and collects the results in a scoreboard.

The tutorial is organized in two parts. The first part introduces XMODEL as a way of modeling and simulating analog circuits in SystemVerilog. The lab exercises will show how to auto-extract a SystemVerilog model from the analog filter circuit and build a SystemVerilog testbench measuring its response to a sinusoidal input using XMODEL primitives. By the end of the first part, you will have your fixture module enclosing the analog DUT and its instrumentations ready.

The second part starts with an intuitive overview of UVM and shows how to put the sequencer, driver, monitor, and scoreboard components around the fixture module to build a UVM testbench. The lab exercises will guide you how to write a sequencer generating a sequence of random frequencies, a driver sending the stimulus data to the fixture module, a monitor receiving the measured responses from the fixture, and finally a scoreboard comparing the results against the SPICE simulation data. By the end of this second part, you will be running simulation with your own UVM testbench verifying the filter’s transfer gains at randomly-chosen frequencies.

No strong background is required either in analog circuits or digital verification. Each concept, feature, or technique is introduced in a step-by-step fashion and anyone with a basic knowledge of SystemVerilog is welcome to attend. To attend this tutorial, register at DVCon US 2023 website: https://dvcon.org/registration.

1. Jaeha Kim

Professor, Seoul National University, Korea / C.E.O. & Founder, Scientific Analog, Inc., Palo Alto, CA

Jaeha Kim is currently Professor at Seoul National University (SNU), Seoul, Korea and founded Scientific Analog, Inc. in 2015, developing EDA tools for analog/mixed-signal modeling and simulation in SystemVerilog. He received the B.S. degree in electrical engineering from Seoul National University in 1997, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University in 1999 and 2003, respectively. Prior to joining SNU, Prof. Kim was with Stanford University as Acting Assistant Professor, with Rambus, Inc. as Principal Engineer, and with Inter-university Semiconductor Research Center (ISRC) at SNU as Post-doctoral Researcher. Prof. Kim is a recipient of the Takuo Sugano award for outstanding far-east paper at 2005 ISSCC and cited as Top 100 Technology Leader of Korea in 2020 by the National Academy of Engineering of Korea. He is an IEEE SSCS Distinguished Lecturer and Associate Editor of IEEE Journal of Solid-State Circuits (JSSC).

2. Charles Dančak

Verification Instructor and Consultant, Betasoft Consulting, Inc.

Charles Dančak is a trainer and consultant based in Silicon Valley. He holds two MS degrees, one in electrical engineering and one in solid-state physics. Charles began his career as a technology engineer in one of Intel’s wafer fabs and spent ten years at Synopsys developing hands-on courses on HDL-based design, simulation, and DFT. He introduced the first SystemVerilog workshop in the University of California Extension system in 2007 and still teaches SystemVerilog online, currently with UC San Diego Extension (ECE-40301). Recently, Charles presented a paper on UVM for analog/mixed-signal verification at DVCon U.S. 2022.