January 28th, 2023

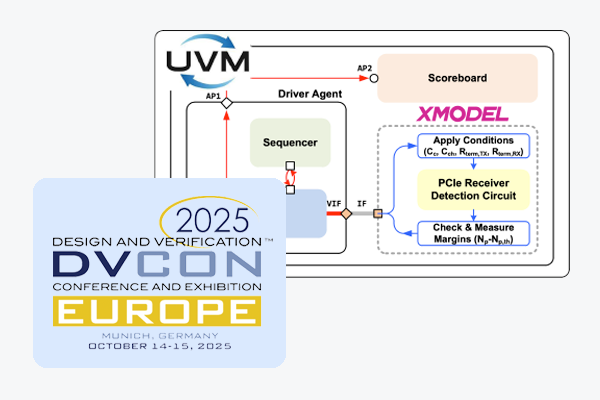

Scientific Analog, Inc. congratulates the researchers of Seoul National University, Seoul, Korea on the recent acceptance of their paper to the 2023 Design and Verification Conference & Exhibition United States (DVCON U.S.), sponsored by Accellera Systems Initiative. The conference will be held in-person on February 27-March 2, 2023 at Double-Tree by Hilton Hotel in San Jose, CA, U.S.A.

The accepted paper is titled, “A UVM Reactive Testbench for Jitter Tolerance Measurement of High-Speed Wireline Receivers,” and describes a UVM testbench that can measure the jitter tolerance characteristics of a high-speed wireline receiver model described in SystemVerilog. The measurement of jitter tolerance requires an iterative search and the testbench extends the reactive stimulus technique of UVM to find the maximum sinusoidal jitter that can be tolerated by the receiver system. The paper will be presented during the poster session scheduled at 11:00am on Tuesday, February 28, 2023.

Scientific Analog, Inc. is a leading developer and provider of a mixed-signal simulator in SystemVerilog (XMODEL), automatic model generator (MODELZEN), and schematic-based design environment (GLISTER). DVCon is the premier conference for discussion of the functional design and verification of electronic systems. DVCon is sponsored by Accellera Systems Initiative, an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP) and electronic design automation (EDA) companies.

All the trademarks used in this press release are the property of their respective holders.

Latest Issues

February 24th, 2026

Meet XMODEL at DVCon U.S. 2026

December 24th, 2025

Happy Holidays! May you find a question that makes all the difference in 2026

October 29th, 2025

Founder of Scientific Analog Receives the Prestigious Doyeon-Changjo Award

October 14th, 2025