PRIMITIVE OF THE MONTH

interp_xbit

This primitive models a digital buffer stage, of which output transition time is determined by a weighted interpolation of the two inputs' arrival times.

PRIMITIVE OF THE MONTH

This primitive models a digital buffer stage, of which output transition time is determined by a weighted interpolation of the two inputs' arrival times.

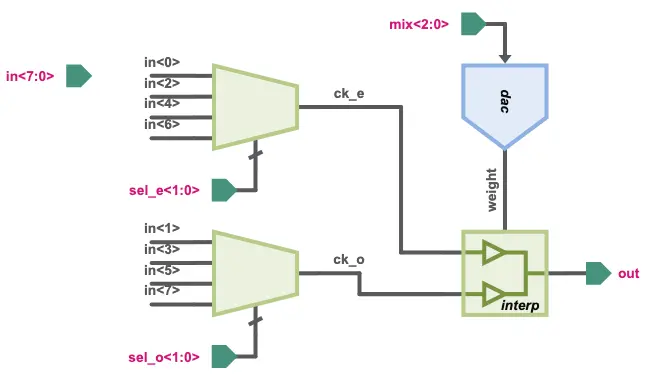

MODEL OF THE MONTH

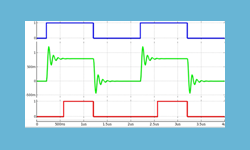

Check out how you can model a digitally-controlled phase interpolator stage found in many clock-and-data recovery (CDR) circuits by combining the 'interp_xbit' and 'dac' primitives.

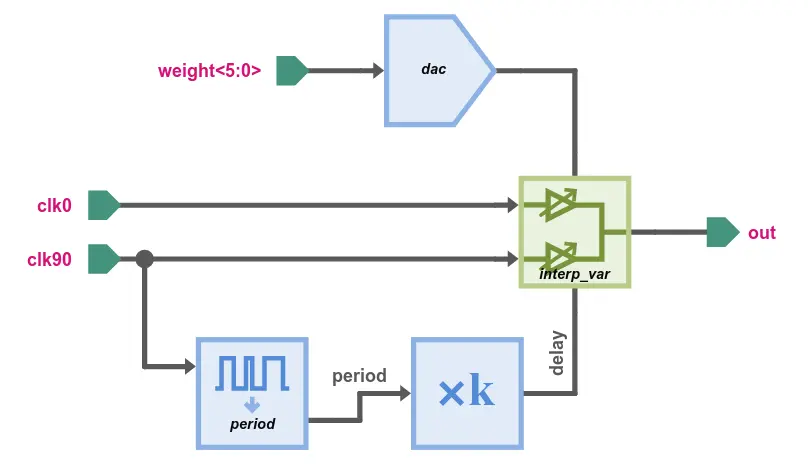

TIP OF THE MONTH

Learn how to use an 'interp_var_xbit' primitive to model a phase interpolator that operates over a wide frequency range.

EQCHECK, Adaptive Decision-Feedback Equalizer, and More

XMODEL at DVCon US, Introducing EQCHECK, and More

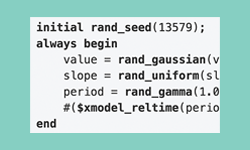

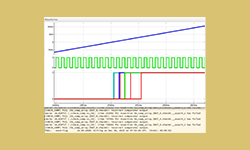

Generating Random Step Sequences for Stress-Testing, Measuring Single-Bit Responses, and More

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More