Primitive of the Month

probe_dc

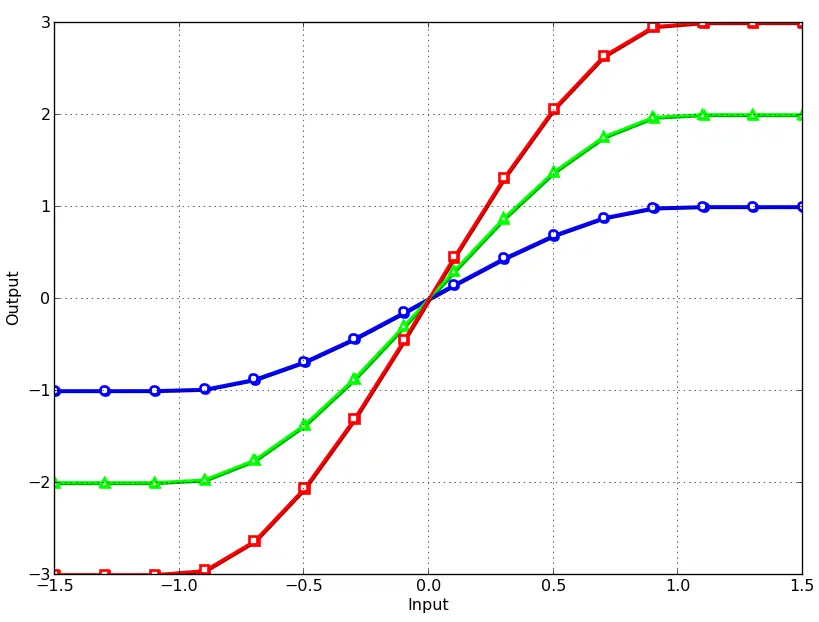

This primitive lets you measure the DC transfer function of your circuit model in a single simulation run.

This primitive lets you measure the DC transfer function of your circuit model in a single simulation run.

Learn how to perform DC analysis on your model and plot its DC transfer function using the new 'probe_dc' primitive and 'meas_dc' script.

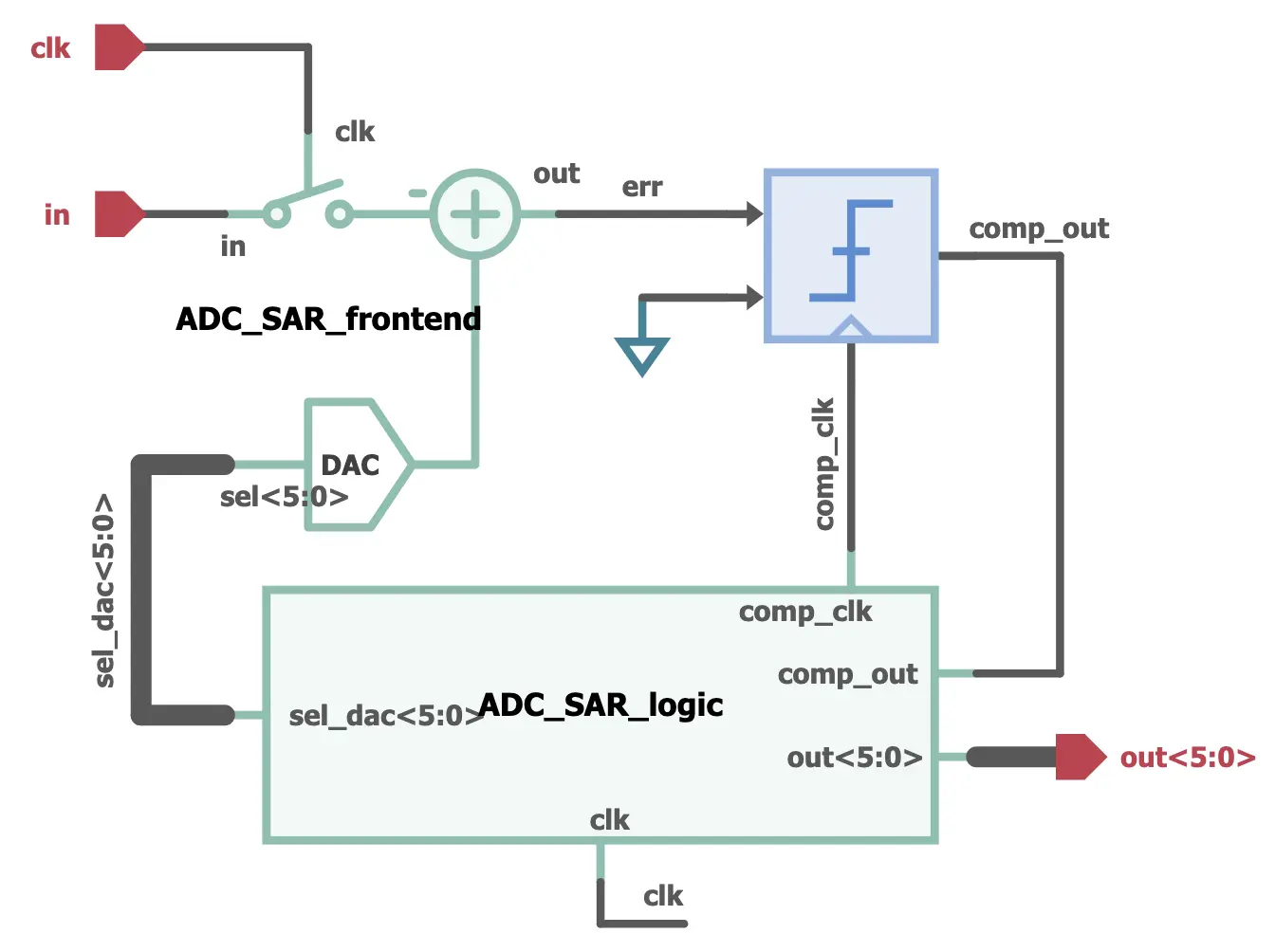

Check out how to model a SAR ADC made of a charge-redistribution DAC and successive approximation FSM.

This release introduces 'probe_dc' primitive, adds multiprocessing support for UDMs, and generates parameterized symbol views for Verilog modules with variable port widths.

EQCHECK, Adaptive Decision-Feedback Equalizer, and More

XMODEL at DVCon US, Introducing EQCHECK, and More

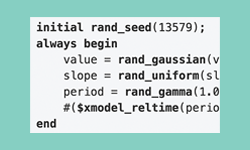

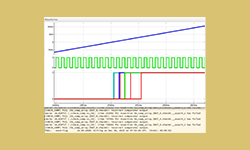

Generating Random Step Sequences for Stress-Testing, Measuring Single-Bit Responses, and More

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

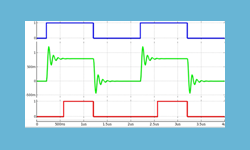

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More