Model of the Month

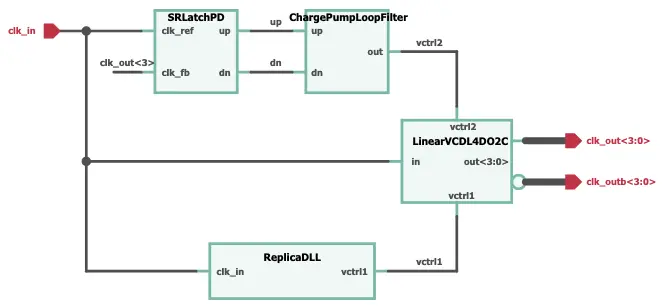

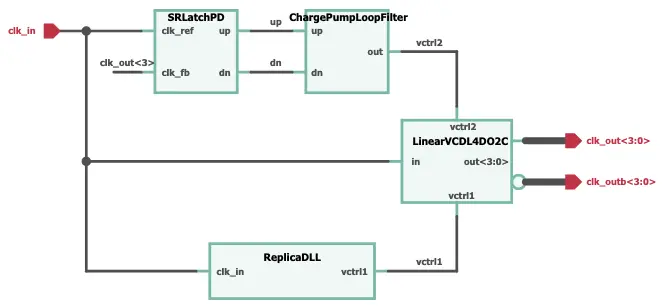

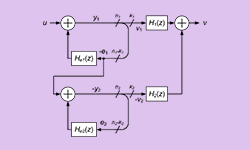

DLL with a replica loop

Check out this model for a delay-locked loop (DLL) that operates over a wide frequency range without false locks using a replica loop, published by Y. Moon, et al. in 2000.

Check out this model for a delay-locked loop (DLL) that operates over a wide frequency range without false locks using a replica loop, published by Y. Moon, et al. in 2000.

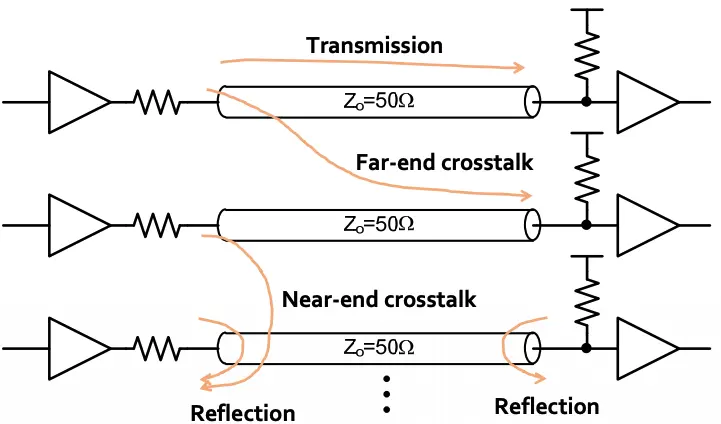

With the new 'sparam_to_tline' utility, you can now extract a multi-port transmission line model including all the port-to-port transfer functions such as reflections and crosstalks from an S-parameter file.

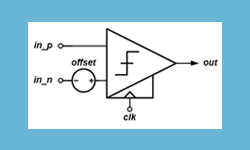

This primitive models a D-flipflop, with optional setup and hold time violation checks.

This release adds the support for UDM mappings on individual slices of parallel instances, and internal current probing for variable RLC and switch primitives.

XMODEL at DAC 2025, Modeling an Asynchronous SAR-ADC, and More

Modeling NAND Flash Memory, Measuring Comparator's Offset, and More

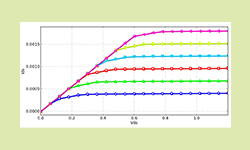

Silicon Photonics Simulation with XMODEL, Measuring I-V Curves, and More

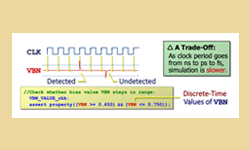

Catching Elusive Voltage Spikes with Assertions, Modeling VCO with Extra Digital Inputs, and More

Modeling Delta-Sigma Digital-to-Analog Converters, XMODEL at DVCon US, and More