Upcoming Event

Meet XMODEL at DAC 2022

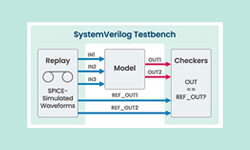

Meet our experts in person and learn why XMODEL is the best way to verify analog circuits in SystemVerilog!

Meet our experts in person and learn why XMODEL is the best way to verify analog circuits in SystemVerilog!

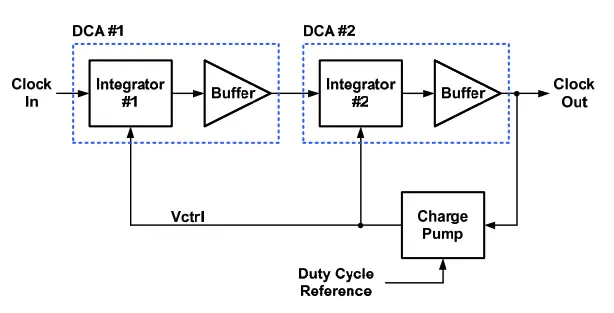

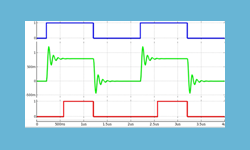

This application note models the duty-cycle corrector presented by James S. Humble, et al., in their 2006 ISSCC paper.

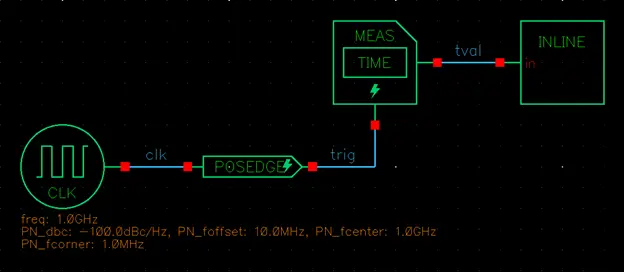

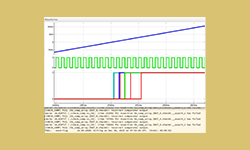

Check out how to dump the time instants of the clock's transition edges into a text file for post-processing.

This primitive measures the time of each input event being triggered.

This release improves the XMODEL's stability of circuit-level simulation and the MODELZEN support for CDL-format netlists.

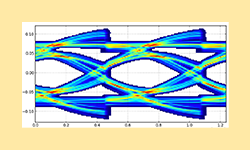

EQCHECK, Adaptive Decision-Feedback Equalizer, and More

XMODEL at DVCon US, Introducing EQCHECK, and More

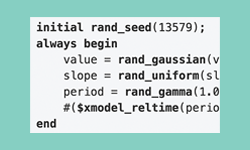

Generating Random Step Sequences for Stress-Testing, Measuring Single-Bit Responses, and More

Season's Greetings, Checking a Clocked Comparator's Correct Output, and More

Checking the Settling of an Analog Signal, Handling Inherited Nets with Legacy SPICE Netlisters, and More