November 28th, 2022

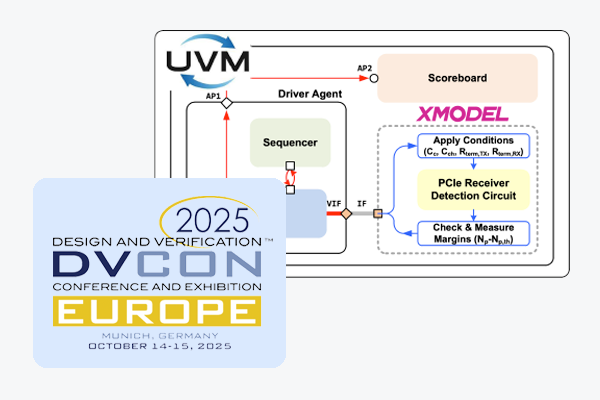

Scientific Analog, Inc. is pleased to announce that the researchers of Seoul National University, Seoul, Korea will be presenting a paper titled, "A UVM SystemVerilog Testbench for 5G/LTE Multi-Standard RF Transceiver," at the upcoming 2022 Design and Verification Conference and Exhibition Europe (DVCon Europe 2022), held in Munich, Germany on December 6-7, 2022.

The paper demonstrates how to use UVM to thoroughly verify a highly-reconfigurable analog/mixed-signal system supporting 351 operating modes. By describing a fixture module enclosing the multi-standard RF transceiver model and the analog instrumentations to supply stimuli and measure responses using XMODEL primitives, one can compose the rest of the testbench using standard UVM components, performing data checks, connectivity checks, and control signal checks with 100% coverage. The paper will be presented at 13:15pm on Wednesday, December 7, 2022 in Session P1.2.

"This paper provides a clear evidence that XMODEL is the best way to verify large-scale analog/mixed-signal systems in SystemVerilog," said Jaeha Kim, CEO and founder of Scientific Analog.

Scientific Analog, Inc. is a leading developer and provider of a mixed-signal simulator in SystemVerilog (XMODEL), automatic model generator (MODELZEN), and schematic-based design environment (GLISTER). DVCon is the premier conference for discussion of the functional design and verification of electronic systems. DVCon is sponsored by Accellera Systems Initiative, an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP) and electronic design automation (EDA) companies.

All the trademarks used in this press release are the property of their respective holders.

Latest Issues

February 24th, 2026

Meet XMODEL at DVCon U.S. 2026

December 24th, 2025

Happy Holidays! May you find a question that makes all the difference in 2026

October 29th, 2025

Founder of Scientific Analog Receives the Prestigious Doyeon-Changjo Award

October 14th, 2025