Tutorial on Demand

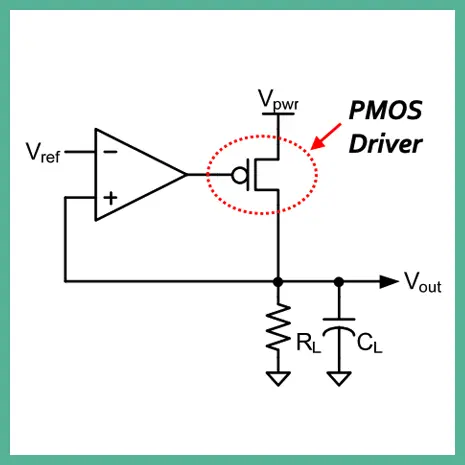

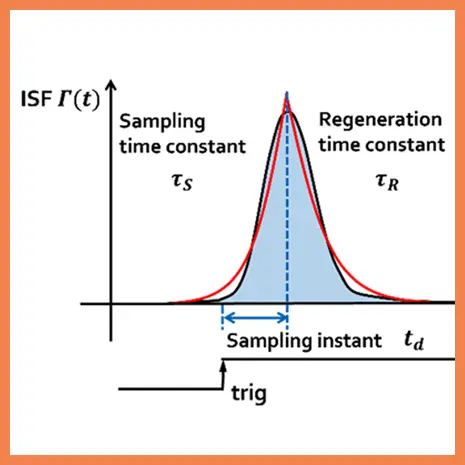

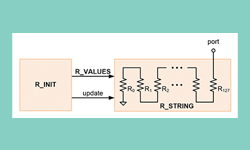

Low Drop-Out (LDO) Regulator Modeling

Watch this video and learn how to model LDO regulator circuits and simulate them in SystemVerilog.

Watch this video and learn how to model LDO regulator circuits and simulate them in SystemVerilog.

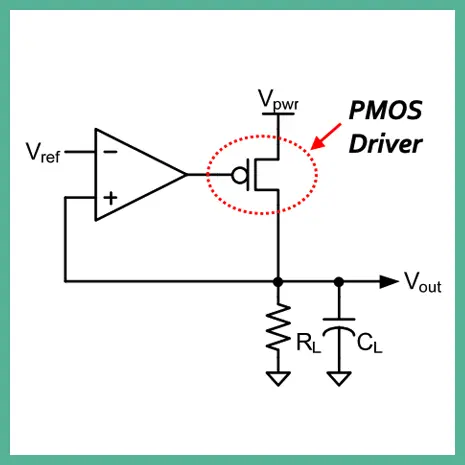

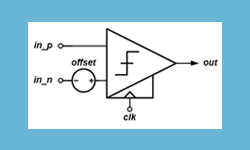

'compare' primitiveDid you know the 'compare' primitive has a finite-aperture mode, which can model a clocked comparator with finite sampling bandwidth and regeneration time?

This primitive is equivalent to a pair of anti-parallel clamping diodes, which can keep the voltage between two circuit nodes within specified limits.

This release adds important bug fixes for XMODEL primitives and improves the support for mapping UDMs via technology configuration file.

XMODEL at DAC 2025, Modeling an Asynchronous SAR-ADC, and More

Modeling NAND Flash Memory, Measuring Comparator's Offset, and More

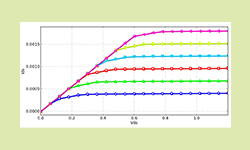

Silicon Photonics Simulation with XMODEL, Measuring I-V Curves, and More

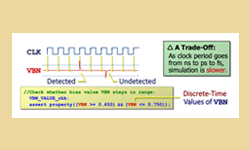

Catching Elusive Voltage Spikes with Assertions, Modeling VCO with Extra Digital Inputs, and More

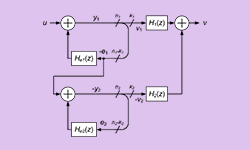

Modeling Delta-Sigma Digital-to-Analog Converters, XMODEL at DVCon US, and More