Model of the Month

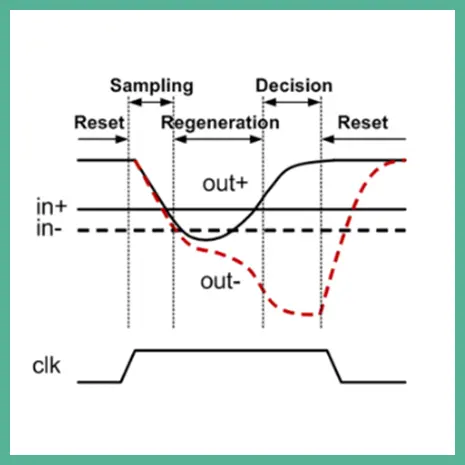

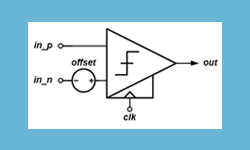

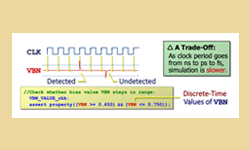

Modeling a clocked comparator latch with reset, sampling, and regeneration behaviors

Can you model a regenerative amplifier with analog outputs performing reset, sampling, and regeneration? No, a transistor-level model doesn’t count.